This product, formerly sold by ams AG, and before that optionally by either Applied Sensors GmbH, acam-messelectronic GmbH or Cambridge CMOS Sensors, is now owned and sold by

## ScioSense

The technical content of this document under ams / Applied Sensors / acammesselectronic / Cambridge CMOS Sensors is still valid.

Contact information Headquarters: Sciosense B.V. High Tech Campus 10 5656 AE Eindhoven The Netherlands info@sciosense.com www.sciosense.com

## acam-messelectronic gmbH

is now

## Member of the ams Group

The technical content of this acam-messelectronic document is still valid.

**Contact information:**

Headquarters:

ams AG Tobelbader Strasse 30 8141 Premstaetten, Austria Tel: +43 (0) 3136 500 0 e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

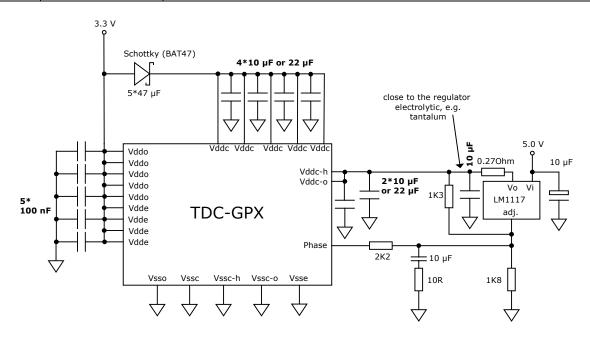

## TDC-GPX - Reduced Decoupling

This note is a supplement to application note no. 13, "TDC-GPX - PLL Regulation Circuit"

The intention is to show possibilities to reduce the number and size of the decoupling capacitors in the TDC-GPX supply circuit. We propose the following capacitors for the different power supply blocks:

| 1. | Vddo             | Data bus I/O supply | TQFP pins 17, 40, 54<br>FBGA pins G3, L6, L12                                                                                                                                                                                                                                                                                                                                                                 | 100 nF per pin                                                                                                            |

|----|------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 2. | Vddo             | I/O supply          | TQFP pins 2,98,94,91,86,82,81,77<br>FBGA pins B1,A3,C4,C5,B7,A9,B9,A11                                                                                                                                                                                                                                                                                                                                        | Connect all pins to a common copper plane<br>and place two 100nF capacitors close to pins<br>77/A11 and 98/A3             |

| 3. | Vddc             | Core supply         | TQFP pins 1, 10, 39, 69, 79<br>FBGA pins A1, F1, M7, E12, B10                                                                                                                                                                                                                                                                                                                                                 | Connect a capacitor to each side of the chip<br>TQFP pins 10, 39, 69, 79<br>FBGA pins F1, M7, E12, B10                    |

|    |                  |                     | Standard: 4 x 47 $\mu$ F<br>Derating (increase of standard deviation<br>4 x 10 $\mu$ F<br>up to 200ns: no effect<br>up to 500ns: about 4ps<br>up to 1000ns: about 15ps                                                                                                                                                                                                                                        | a) with smaller capacities:<br>4 x 22 μF<br>up to 200ns: no effect<br>up to 500ns: about 2 ps<br>up to 1000ns: about 7 ps |

| 4. | Vddc-o<br>Vddc-h | Hardmacro supply    | TQFP pins 87, 88<br>FBGA pins C6, A7                                                                                                                                                                                                                                                                                                                                                                          | One capacitor to each pin and the voltage regulator output                                                                |

|    |                  |                     | Standard: 1 x 100 $\mu$ F at regulator out and 2 x 47 $\mu$ F at the pinsThe regulator decoupling can be reduced to 10 $\mu$ F without a negative effectDerating (increase of standard deviation) with smaller capacities at the pins:2 x 10 $\mu$ F2 x 22 $\mu$ Fup to 200ns: no effectup to 200ns: no effectup to 500ns: about 4 psup to 500ns: about 2 psup to 1000ns: about 10 psup to 1000ns: about 5 ps |                                                                                                                           |