This product, formerly sold by ams AG, and before that optionally by either Applied Sensors GmbH, acam-messelectronic GmbH or Cambridge CMOS Sensors, is now owned and sold by

# ScioSense

The technical content of this document under ams / Applied Sensors / acammesselectronic / Cambridge CMOS Sensors is still valid.

Contact information Headquarters: Sciosense B.V. High Tech Campus 10 5656 AE Eindhoven The Netherlands info@sciosense.com www.sciosense.com

#### acam-messelectronic gmbH

is now

# Member of the ams Group

The technical content of this acam-messelectronic document is still valid.

**Contact information:**

Headquarters:

ams AG Tobelbader Strasse 30 8141 Premstaetten, Austria Tel: +43 (0) 3136 500 0 e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

# TDC-GPX PLL Regulation Circuits

16th September 2010 Document-No.: AN013\_e V3.0

#### Introduction:

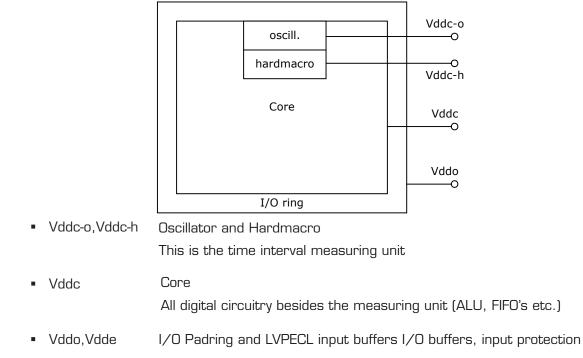

The TDC-GPX chip shows different blocks with separate power supplies:

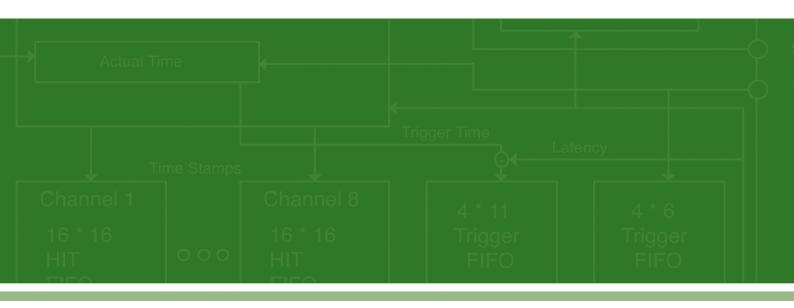

Figure 1 TDC-GPX power supply blocks

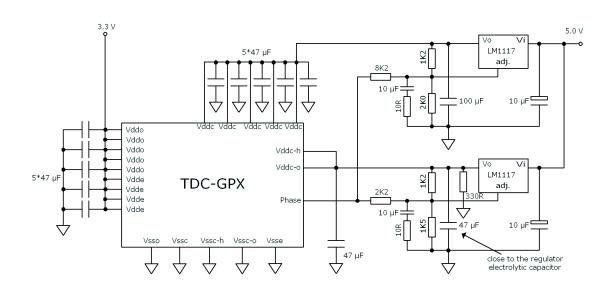

The purpose of the PLL regulation circuit is to keep the speed of the oscillator & hardmacro constant by regulating the voltage Vddc-o/h between 2.4 and 3.6V.

#### Note:

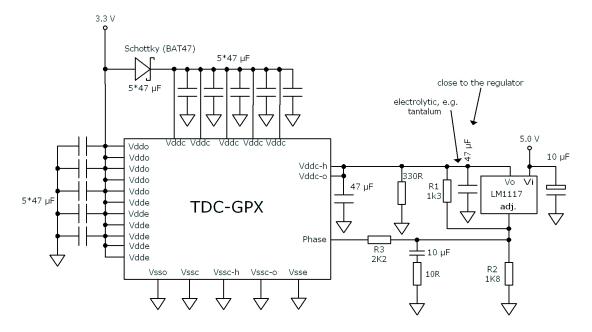

The recommended circuit is based on the LM1117. We strongly recommend to use only LM317 or LM1117 regulators. Only for these regulators the ciruit is tested and approved. Do not use low-drop regulators. This regulator's reference refers to the output voltage.

#### **TDC-GPX**

Figure 2: Circuit with one regulator and Schottky diode

The IO buffers are supplied with 3.3V typically to be compatible with a 3.3V design. It is strongly recommended to use a linear regulator to provide the 3.3V. Switched mode regulators will introduce a lot of noise to the measurement. The core voltage is set to 3.0V. The easiest way to do this is to use a BAT47 schottky diode. The purpose is to avoid voltage differences bigger than 0.6V between Vddc and Vddo on the one side and Vddc and Vddc-o/h on the other. The outputs' high-side switches do not fully close when Vddc is more than 0.6V below Vddo. Therefore other devices on the bus must be able to drive a few mA to pull the outputs down to LOW. This may be no problem for an FPGA and only one TDC-GPX connected to the bus. But of course

this is a problem with weak drivers and more than one device on a bus.

## TDC

#### TDC-GPX

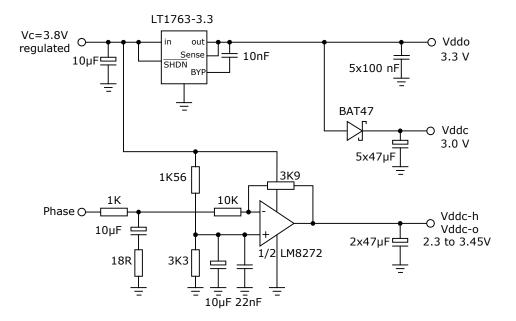

#### **Calculating the Resistors**

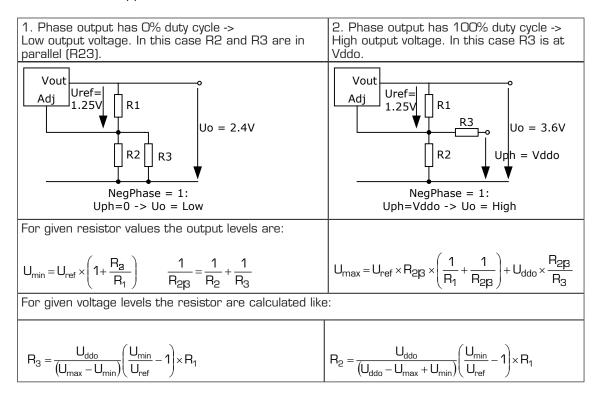

In the TDC-GPX application we look at two extremes:

### **Blocking Capacitors**

|    | r                | T                   |                                                                                                                                                                                                                                                                                                                                                                                                             | r                                                                                                                             |

|----|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 1. | Vddo             | Data bus I/O supply | TQFP pins 17, 40, 54<br>FBGA pins G3, L6, L12                                                                                                                                                                                                                                                                                                                                                               | 100 nF per pin                                                                                                                |

| 2. | Vddo             | I∕O supply          | TQFP pins<br>2,98,94,91,86,82,81,77<br>FBGA pins<br>B1,A3,C4,C5,B7,A9,B9,A11                                                                                                                                                                                                                                                                                                                                | Connect all pins to a common<br>copper plane and place two<br>100nF capacitors close to<br>pins 77/A11 and 98/A3              |

| З. | Vddc             | Core supply         | TQFP pins 1, 10, 39, 69, 79<br>FBGA pins A1, F1, M7, E12,<br>B10                                                                                                                                                                                                                                                                                                                                            | Connect a capacitor to each<br>side of the chip<br>TQFP pins 10, 39, 69, 79<br>FBGA pins F1, M7, E12, B10                     |

|    |                  |                     | Standard: $4 \times 47 \mu$ F<br>Derating (increase of standard<br>ties:<br>$4 \times 10 \mu$ F<br>up to 200ns: no effect<br>up to 500ns: about 4ps<br>up to 1000ns: about 15ps                                                                                                                                                                                                                             | deviation) with smaller capaci-<br>4 x 22 μF<br>up to 200ns: no effect<br>up to 500ns: about 2 ps<br>up to 1000ns: about 7 ps |

| 4. | Vddc-o<br>Vddc-h | Hardmacro supply    | TQFP pins 87, 88<br>FBGA pins C6, A7                                                                                                                                                                                                                                                                                                                                                                        | One capacitor to each pin and the voltage regulator output                                                                    |

|    |                  |                     | Standard: 1 x 47 $\mu$ F at regulator out and 1 x 47 $\mu$ F at the<br>pins.The regulator decoupling can be reduced to 10 $\mu$ F without a<br>negative effectDerating (increase of standard deviation) with smaller capaci-<br>ties at the pins:2 x 10 $\mu$ F2 x 22 $\mu$ F<br>up to 200ns: no effectup to 200ns: no effectup to 200ns: no effect<br>up to 500ns: about 4 ps<br>up to 1000ns: about 10 ps |                                                                                                                               |

# TDC

#### TDC-GPX

#### **Extended Regulation Range**

The solution from above shows a slightly reduced regulation range. The reason is that the oscillator speed at Vddc-o/h = 3.6V & Vddc = 3.0V is a little bit less than with both voltages at 3.6V.

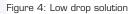

There is a solution to overcome this: using a second regulation circuit for Vddc instead of the schottky diode. The second regulator for Vddc has a regulation range from 3.0V to 3.6V. In other words: With TDC-GPX output phase=LOW regulator 1 delivers Vddc-o/h = 2.4V and regulator 2 delivers Vddc=3.0V. At phase=HIGH regulator 1 delivers Vddc-o/h = 3.6V and regulator 2 delivers Vddc=3.6V. Of course the circuit is alittle bit more complex.

Figure 3 Circuit with two regulators for extended regulation range

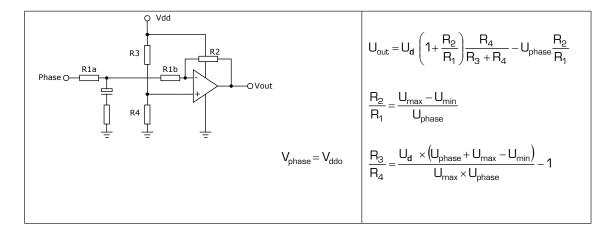

#### **Low-drop Solution**

The recommended circuit from above doesn't work with low-drop regulators. In applications where the power dissipation has to be as low as possible the following circuit can be used. In this circuit the voltage regulator is replaced by an operational amplifier.

The LM8272 has enough output power and is ecspecially designed to drive high capacitive loads.

acam-messelectronic gmbh Am Hasenbiel 27 76297 Stutensee-Blankenloch Germany / Allemagne ph. +49 7244 7419 - 0 fax +49 7244 7419 - 29 e-mail: support@acam.de www.acam.de