This product, formerly sold by ams AG, and before that optionally by either Applied Sensors GmbH, acam-messelectronic GmbH or Cambridge CMOS Sensors, is now owned and sold by

# ScioSense

The technical content of this document under ams / Applied Sensors / acammesselectronic / Cambridge CMOS Sensors is still valid.

Contact information

Headquarters:

ScioSense B.V.

High Tech Campus 10

5656 AE Eindhoven

The Netherlands

info@sciosense.com

www.sciosense.com

## TDC-GPX

Ultra-high Performance 8 Channel Time-to-Digital Converter

## **Datasheet**

$Jan\ 18^{\mbox{\tiny TH}}$  , 2007

## acam - solutions in time

Precision Time Interval Measurement

## 1. Introduction

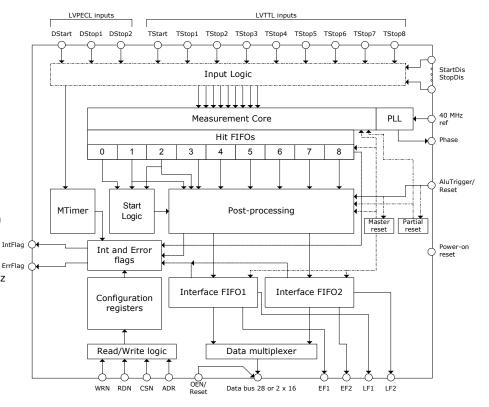

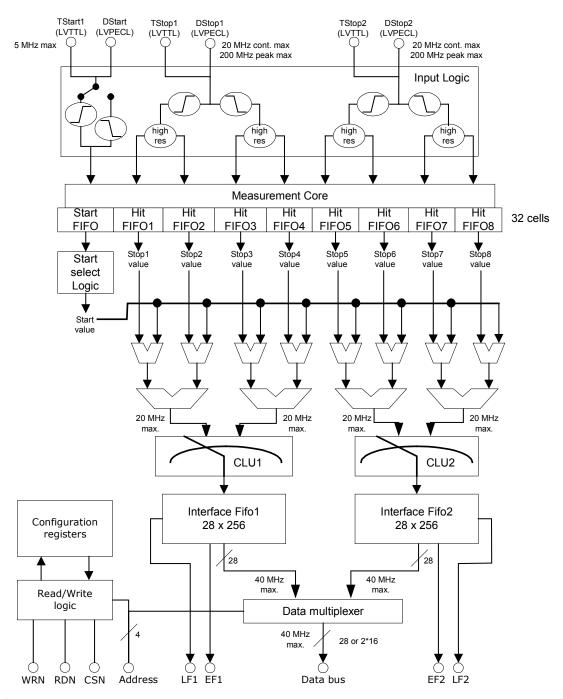

## 1.1 System overview

- 8 channels with typ. 81 ps resolution

- 9 LVTTL inputs, optional 3 LVPECL inputs

- 5.5 ns pulse-pair resolution with 32-fold multi-hit capability = 182 MHz peak rate

- Trigger to rising or falling edge

- Measurement range 9,8 µs, endless measurement range by internal retrigger of START

- 10 MHz continuous rate per channel

- 40 MHz continuous rate per chip

#### G-Mode

- 2 channels with 40 ps resolution

- Differential LVPECL inputs, optional LVTTL

- Measurement range 0 ns to 65 μs

- 5.5 ns pulse-pair resolution between edges of equal slope with 32-fold multi-hit = 182 MHz peak rate

- Minimum pulse width 1.5 ns

- Trigger to rising <u>and</u> falling edge

- Optional Quiet Mode (no ALU operation and Dataoutput during measurements)

- 20 MHz continuous rate per channel

- 40 MHz continuous rate per chip

#### R-Mode

- 2 channels with 27 ps resolution

- Differential LVPECL inputs, optional LVTTL

- Measurement range 0 μs up to 40 μs

- 5.5 ns pulse-pair resolution with 32-fold multi-hit capability = 182 MHz peak rate

- Trigger to rising or falling edge

- Optional Quiet Mode (no ALU operation and Dataoutput during measurements)

- 40 MHz continuous rate per channel

- 40 MHz continuous rate per chip

#### M-Mode

- 2 channels with 10 ps resolution (70 ps peak-peak)

- Differential LVPECL inputs

- Measurement range 0 ns up to 10 μs

- Single hit per Start and channel

- Trigger to rising or falling edge

- Quiet Mode (no ALU operation and Data-output during measurements)

- Max. 500 kHz continuous rate per channel

- Max. 1 MHz continuous rate per chip

## General

- Start retrigger option (besides M-Mode)

- Packages: TQFP100, TFBGA120

- IO voltage 3.0 V 3.6 V

- Core voltage 2.3 V 3.6 V regulated by resolution adjust unit

- Data bus: 28 Bit or 2 x 16 Bit asynchronous with Chipselect, Readstrobe, Writestrobe

- 40 MHz continuous rate per chip

- Address range: 4 Bit

## 1.2 Index

| 1. | Introduction                       | 3  |

|----|------------------------------------|----|

|    | 1.1 System overview                | 3  |

|    | 1.2 Index                          | 4  |

|    | 1.3 Electrical Characteristics     | 6  |

|    | 1.3.1 Bus Timings                  | 7  |

|    | 1.3.2 16 Bit Mode                  | 8  |

|    | 1.3.3 Disable Timings              | 9  |

|    | 1.3.4 Reset Timings                | 9  |

|    | 1.3.5 General Timings & Resolution |    |

|    | 1.4 Pin Description                | 11 |

|    | 1.5 Package Drawings               |    |

|    | 1.6 Power supply                   |    |

|    | 1.6.1 Resolution adjust            | 15 |

|    | 1.6.2 Supply voltages              |    |

|    | 1.6.3 Design Rules                 |    |

|    | 1.7 Register settings              |    |

|    | 1.7.1 Write Registers              |    |

|    | 1.7.2 Read registers               | 19 |

|    | 1.7.3 Read/Write registers         |    |

| _  | Ç                                  |    |

| 2  | I-Mode                             | 22 |

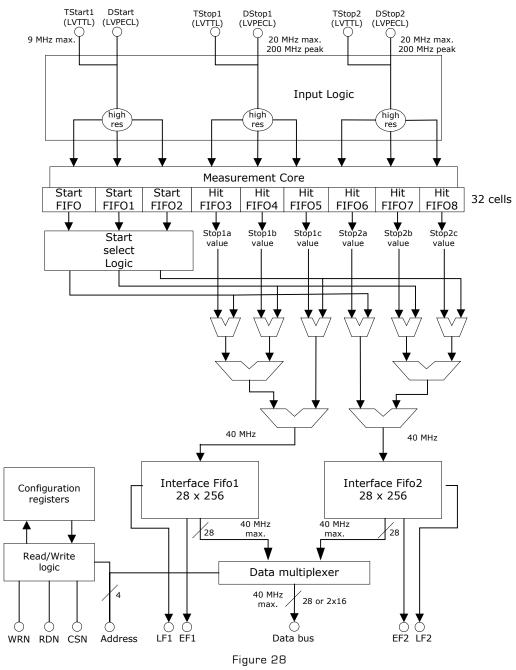

|    | 2.1 Block diagram I-Mode           |    |

|    | 2.2 Input circuitry I-Mode         |    |

|    | 2.3 I-Mode Basics                  |    |

|    | 2.4 Data structure                 |    |

|    | 2.5 Reset                          |    |

|    | 2.6 MTimer                         |    |

|    | 2.7 Interrupt Flag                 |    |

|    | 2.8 Error Flag                     |    |

|    | 2.9 Differential Inputs.           |    |

|    | 2.10 I-Mode Timing & Resolution    |    |

|    | 2.11 Measurement Flow              |    |

|    | 2.11.1 Single measurement          |    |

|    | 2.11.2 Continous Measurement       | 29 |

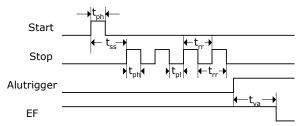

| 3  | G-Mode                             | 30 |

| _  | 3.1 Block diagram G-Mode           |    |

|    | 3.3 G-Mode Basics.                 |    |

|    | 3.4 Data structure and readout     |    |

|    | 3.5 Reset                          |    |

|    | 3.6 MTimer                         |    |

|    | 3.7 Interrupt Flag                 |    |

|    | 3.8 Error Flag                     |    |

|    | 3.9 Testinputs                     |    |

|    | 3.10 RaSpeed & Delx                |    |

|    | 3.11 G-Mode Timing & Resolution    |    |

|    | 3.12 Measurement Flow              |    |

|    |                                    |    |

| 4  | R-Mode                             | 37 |

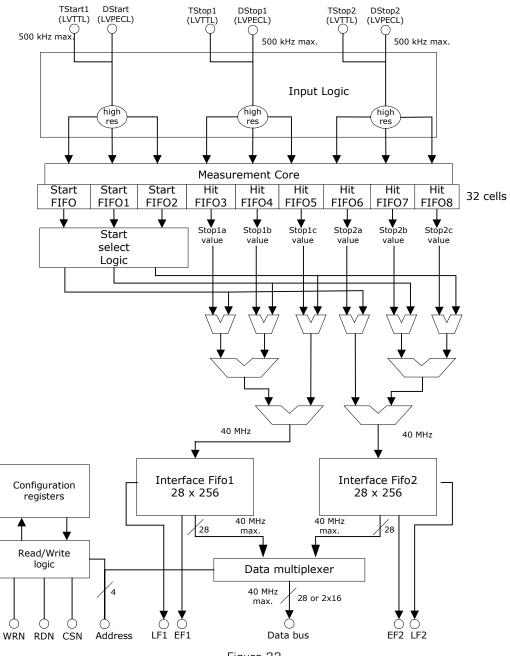

|    | 4.1 Block diagram R-Mode           |    |

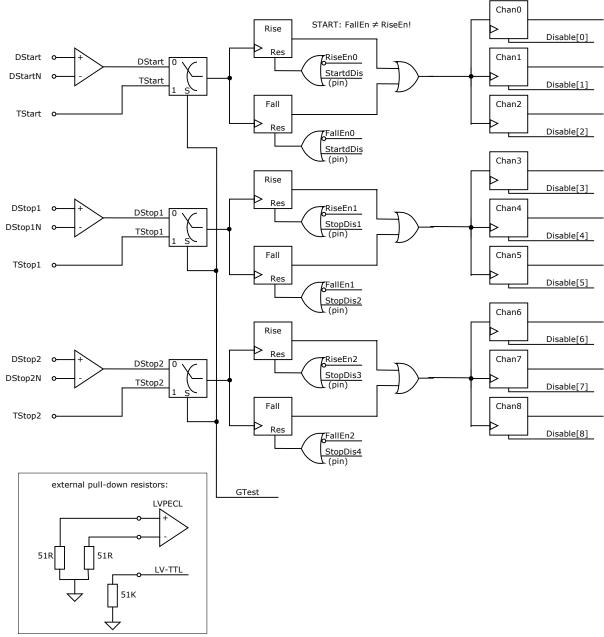

|    | 4.2 Input Circuitry R-Mode         |    |

|    | 4.3 R-Mode Basics                  | 39 |

| 4.4 Data structure and readout  | 41             |

|---------------------------------|----------------|

| 4.5 Reset                       |                |

| 4.6 MTimer                      | 41             |

| 4.7 Interrupt Flag              | 41             |

| 4.8 Error Flag                  |                |

| 4.9 Testinputs                  | 41             |

| 4.10 RaSpeed & Delx             | 41             |

| 4.11 R-Mode Timing & Resolution | 42             |

| 4.12 Measurement Flow           | 43             |

| 5 M-Mode                        | 45             |

|                                 | - <del>-</del> |

| 5.1 Block diagram M-Mode        |                |

| 5.2 Input Circuitry M-Mode      |                |

| 5.3 M-Mode Basics               |                |

| 5.4 Data structure and readout  | 48             |

| 5.5 Reset                       | 48             |

| 5.6 MTimer                      | 49             |

| 5.7 Interrupt Flag              |                |

| 5.8 Error Flag                  |                |

| 5.9 Testinputs                  |                |

| 5.10 M-Mode Timing & Resolution |                |

| 5.11 Measurement Flow           |                |

|                                 |                |

| 6 Bug Report                    | 51             |

| 6.1 Data Bus: 16 Bit Mode       | 51             |

| Contract                        | EG             |

## 1.3 Electrical Characteristics

Absolute Maximum Ratings (Vss = OV, Tj = 25°C)

| section individual fractings (vec ev, i) Le e) |                  |        |                    |              |      |

|------------------------------------------------|------------------|--------|--------------------|--------------|------|

| Para                                           | ameter           | Symbol | Condition          | Rated Value  | Unit |

| Supply voltage                                 | 1/0              | Vddo   |                    | -0.3 to +3.6 | V    |

|                                                | Core             | Vddc   | Vdcc < Vddo + 0.6V | -0.3 to +3.6 |      |

|                                                | Hardmacro        | Vddc-h | Vdcc < Vddo + 0.6V | -0.3 to +3.6 |      |

|                                                | Oscillator       | Vddc-o | Vdcc < Vddo + 0.6V | -0.3 to +3.6 |      |

|                                                | Diff. inputs     | Vdde   |                    | -0.3 to +3.6 |      |

| Input voltage                                  | 5V Tolerant      | Vi     | Vddo = +0.3~3.6V   | -0.3 to 6.0  | V    |

|                                                | Buffers          |        |                    |              |      |

| Output current                                 | 1 mA Buffer      | lo     | -                  | -5 to +5     | mΑ   |

|                                                | 4 mA Buffer      |        |                    | -9 to +9     |      |

| Storage                                        |                  | Tstg   |                    | -65 to 150   | °C   |

| temperature                                    |                  | _      |                    |              |      |

| Junction                                       |                  | Tj     |                    | -40 to 125   | °C   |

| temperature                                    |                  |        |                    |              |      |

| Thermal                                        | junction-ambient | Rthj-a | TQFP100            | 96           | K/W  |

| resistance                                     |                  |        | TFBGA120           | 105          |      |

Terminal Capacitance

| Terminal      | Symbol | Condition                          | Ra  | ited Val | ue  | Unit |

|---------------|--------|------------------------------------|-----|----------|-----|------|

|               |        |                                    | Min | Тур      | Max |      |

| Input         | Ci     | measured @Vdd = Vi = Vo = Vss, f = | 1   | 6        | -   | pF   |

| Output        | Co     | 1 MHz, Ta = 25°C                   | 1   | 9        | -   |      |

| Bidirectional | Cio    |                                    | 1   | 10       | -   |      |

DC Characteristics (Vddo =  $3.3 \text{ V} \pm 0.3 \text{ V}$ , Vss = 0 V, Tj =  $-40 \text{ to } +85^{\circ}\text{C}$ )

| Parameter                 | Symbol | Condition             | Ra  | Rated Value |     | Unit |

|---------------------------|--------|-----------------------|-----|-------------|-----|------|

|                           |        |                       | Min | Тур         | Max |      |

| High-level input voltage  | Vih    | TTL 5V tolerant input | 2.0 | -           | 5.5 | V    |

| Low-level input voltage   | Vil    | TTL 5V tolerant input | 0.0 | -           | 0.8 |      |

| High-level output voltage | Voh    |                       | 2.4 |             |     |      |

| Low-level output voltage  | Vol    |                       |     |             | 0.4 |      |

| Supply current            |        |                       |     | Тур         |     |      |

|                           | Vddo   | 1/0                   | 1   | .4 + Bu     | ıs  | mΑ   |

|                           | Vddc   | Core                  |     | 20          |     |      |

|                           | Vddc-h | Hardmacro             |     | 7           |     |      |

|                           | Vddc-o | Oscillator            |     | 4           |     |      |

|                           | Vdde   | Diff. inputs          |     | 19          |     |      |

## LVPECL inputs:

DC Parameters (VDD = 3.3 V±5 %, Tj = 0°C to 125°C)

| Parameter | Val                             | Condition |

|-----------|---------------------------------|-----------|

| VinOS     | Vdde-1.53V < VinOS < Vdde-0.89V | -         |

| VinDF     | 0.2V < VinDF < 2.1V             | -         |

VinOS = Input offset voltage, [Via+Vian]/2

VinDF = Input differential voltage,

Via = Input voltage of A

Vian = Input voltage of AN

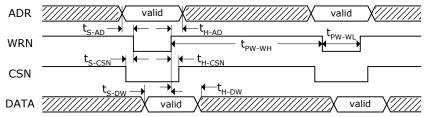

## 1.3.1 Bus Timings

$[Vddo = Vddc = 3.3 V, Ta = +25^{\circ}C]$

## Write operations

Figure 1

| Spec               | Description            | Min (ns) | Max (ns) |

|--------------------|------------------------|----------|----------|

| ts-AD              | Address Setup Time     | 2        | -        |

| t <sub>H-AD</sub>  | Address Hold Time      | 0        | -        |

| t <sub>PW-WL</sub> | Write LOW Time         | 6        | -        |

| t <sub>PW-WH</sub> | Write HIGH Time        | 6        | -        |

| ts-DW              | Write Data Setup Time  | 5        |          |

| t <sub>H-DW</sub>  | Write Data Hold Time   | 4        | -        |

| ts-csn             | Chip Select Setup Time | 0        | -        |

| t <sub>H-CSN</sub> | Chip Select Hold Time  | 0        | -        |

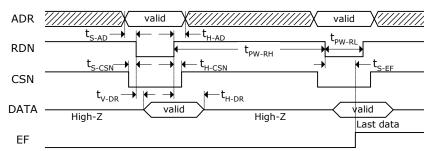

## **Read Operations**

It is not allowed to read from an empty FIFO!

Figure 2

| Spec               | Description            | Min (ns) | Max (ns) |                                                             |

|--------------------|------------------------|----------|----------|-------------------------------------------------------------|

| ts-AD              | Address Setup Time     | 2        | -        | * @ 87ps res. & 40pF load.                                  |

| t <sub>H-AD</sub>  | Address Hold Time      | 0        | -        | This value depends on the                                   |

| t <sub>PW-RL</sub> | Read LOW Time          | 6        | -        | capacitive load and has to be confirmed by evaluation. This |

| t <sub>PW-RH</sub> | Read HIGH Time         | 6        | -        | value also depends on the                                   |

| tv-DR              | Read Data Valid Time   | 5        | 11.8*    | adjusted resolution (e.g)                                   |

| t <sub>H-DR</sub>  | Read Data Hold Time    | 4        | 8.5 * *  |                                                             |

| ts-csn             | Chip Select Setup Time | 0        | -        | ** Can be prolonged infinitely                              |

| t <sub>H-csn</sub> | Chip Select Hold Time  | 0        | -        | with OEN = 0 (driving the bus permanently) and stable ad-   |

| ts-ef              | Empty Flag Set Time    | -        | 11.8*    | dress.                                                      |

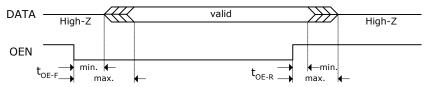

## OEN operations - Driving the bus permanently

Figure 3

| Spec              | Description            | Min (ns) | Max (ns) |

|-------------------|------------------------|----------|----------|

| <b>t</b> oe-F     | OEN Rise to Data Valid | 1.5      | 9        |

| t <sub>OE-R</sub> | OEN Fall to Data Valid | 1        | 8.5      |

**Note:** With OEN = Low the output buffers are driving allthe time, with OEN = High they are driving only during a read strobe. While writing to the TDC-GPX OEN has to be High.

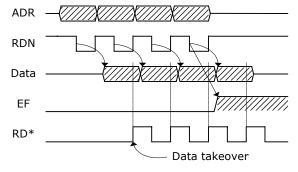

## Fake Reads for speeding up data readout

The maximum data readout rate is limited by the empty flag set time as it is not allowed to read from an empty FIFO. This can be overcome by a second fake read strobe which is delayed to the read strobe at the TDC-GPX.

Figure 4

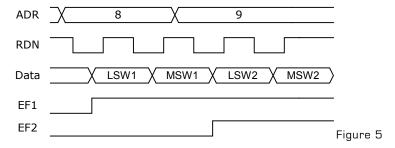

#### 1.3.2 16 Bit Mode

The TDC-GPX data bus can be switched from 28 Bit to 16 Bit. This is done writing a 0x0000010 to address 14. After that all read / write commands have to be done in pairs. When reading the last data from an interface FIFO the empty flag disappears already with the first read command. Nonetheless it is mandatory to read a second time.

The first read/write command always refers to the LSW, the second one to the MSW. The highest 4 Bit of the MSW are not relevant [write] or shall be ignored [read].

Note: See Bug-Report O1 at the end of the datasheet

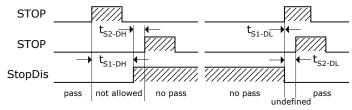

## 1.3.3 Disable Timings

Disable inputs (Vddo = Vddc = 3.3 V, Ta =  $+25^{\circ}\text{C}$ )

| Spec           | Description        | Min  | Max  |

|----------------|--------------------|------|------|

|                |                    | (ns) | (ns) |

| <b>t</b> s1-□H | Disable Setup Time | -    | 6    |

| ts2-DH         | Disable Setup Time | -    | 1    |

| ts1-DL         | Disable Hold Time  | -    | 0    |

| ts2-DL         | Disable Hold Time  | -    | 2    |

Figure 6

StopDisStart (Bit 21, register 5) @ 87 ps resolution

| Spec           | Description                                 | Min (ns) | Max (ns) |

|----------------|---------------------------------------------|----------|----------|

| <b>t</b> s1-DH | Dead Time Rising(Start) to Rising(Stop)     | -        | 6.3      |

| ts2-DH         | Dead Time Falling(Start) to Rising(Stop)    | -        | 6.1      |

| ts1-DL         | Dead Time Rising(Start) to Falling(Stop)    | -        | 5.2      |

| ts2-DL         | Dead Time Falling (Start) to Falling (Stop) | -        | 7.4      |

## 1.3.4 Reset Timings

Power-up Reset: (Vddo = Vddc = 3.3 V, Ta = +25°C)

| Spec            | Description       | Min (ns) | Max (ns) |

|-----------------|-------------------|----------|----------|

| t <sub>ph</sub> | Reset pulse width | 200      | =        |

Master Reset: (Vddo = Vddc = 3.3 V, Ta = +25°C)

| Spec            | Description                                                     | Min (ns) |                            |        |                    |          |

|-----------------|-----------------------------------------------------------------|----------|----------------------------|--------|--------------------|----------|

| t <sub>ph</sub> | Reset pulse width                                               | 10       |                            |        |                    |          |

| trfs            | Time after rising edge of reset pulse before hits are accepted  | 27       | Master Reset<br>(at pin) . |        | t <sub>ph</sub>    |          |

| trrs            | Time after falling edge of reset pulse before hits are accepted | 13       | (at pin)                   |        | → t <sub>rfs</sub> | <b>—</b> |

|                 |                                                                 |          | Start/Stop                 | accept | not acc.           | accept   |

|                 |                                                                 |          |                            | Figure | e 7                |          |

Partial Reset: [Vddo = Vddc = 3.3 V, Ta = +25°C]

| Spec            | Description                                                        | Min (ns) |                                             |

|-----------------|--------------------------------------------------------------------|----------|---------------------------------------------|

| t <sub>ph</sub> | Reset pulse width                                                  | 10       |                                             |

| trfs            | Time after rising edge of reset pulse before hits are accepted     | 60       | Partial Reset (at pin)                      |

| trrs            | Time after falling edge of reset pulse before hits are accepted    | 13       | t <sub>rs</sub> t <sub>rf</sub>             |

| trs             | Time berfore rising edge of reset pulse<br>where hits will be lost | -        | Start/Stop accept not acc. accept  Figure 8 |

## 1.3.5 General Timings & Resolution

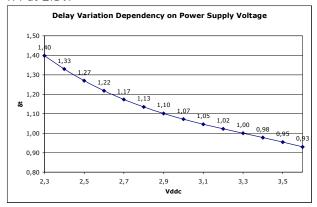

The TDC-GPX time measurement is based on internal propagation delays. Those delays depend on temperature and voltage. They also vary over the production lots. The resolution adjust mode (see) uses the voltage dependency to compensate for temperature and production variations and sets the circuits to a fixed and programmable resolution.

Figure 9 shows the dependency of all timings from the core voltage, referred to the 3.3V timings. The resolution at 3.3V can be varied by factors 0.93 at 3.6V to 1.4 at 2.3V.

Figure 9

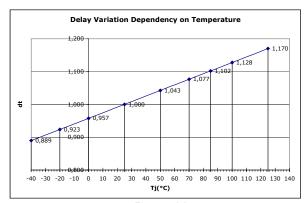

Figure 10 shows the dependency of all timings on the temperature, referred to  $25^{\circ}\text{C}$  junction temperature. If the temperature increases from  $25^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ , the intrinsic resolution goes down by a factor 1.077. In resolution adjust mode this is compensated by increasing the core voltage from 3.3V to 3.6V.

Figure 10

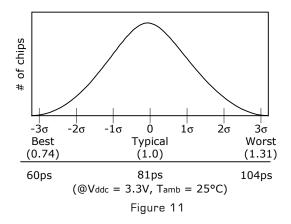

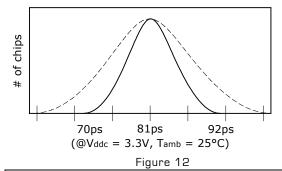

Without resolution adjust, the intrinsic resolution varies slightly from chip to chip. The distribution over the production lots is of gaussian type.

Within a single production lot the distribution is narrower. Figure 12 shows a typical distribution of the intrinsic resolution at 3.3 V core voltage and 25°C ambient temperature within a single production lot.

## Example:

Taking the distribution from Figure 12 and assuming an operating temperature range of 0°C to 40°C as well as 1 Mhz data rate. The junction temperature will be about 57°C max. The slowest chips will have 92ps  $^{\star}$  1.043 = 97ps resolution at 3.3V Vddc. Increasing the core voltage to 3.6V will speed them up to 90.2ps. Setting the resolution adjust mode to a resolution of 95ps will guarantee that the PLLs of all chips will lock at one and the same resolution over the whole operating temperature range.

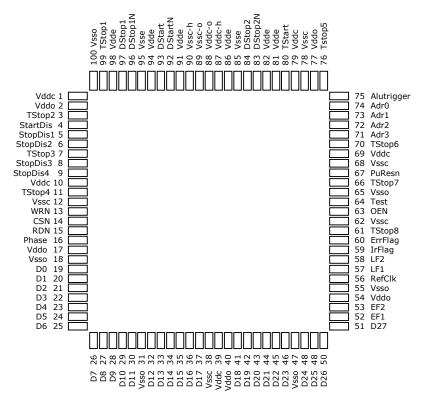

## 1.4 Pin Description

Figure 13

| PIN<br>TQFP<br>100 | No<br>TFBGA<br>120 | PIN Name | Description                                             | Туре      | Terminal () = if not used |

|--------------------|--------------------|----------|---------------------------------------------------------|-----------|---------------------------|

| 001                | A1                 | Vddc     | Core supply voltage                                     |           | Vddc                      |

| 002                | B1                 | Vddo     | I/O supply voltage                                      |           | Vddo                      |

| 003                | C1                 | Tstop2   | TTL input 'Stop2'                                       | TTL input | (10kΩ to GND)             |

| 004                | C2                 | StartDis | Disable input 'DStart' or 'TStart'                      | TTL input | (GND)                     |

| 005                | D1                 | StopDis1 | Disable input 'DStop1' or inputs 'TStop1 ' and 'TStop2' | TTL input | (GND)                     |

| 006                | C3                 | StopDis2 | Disable input 'DStop2' or inputs 'TStop3 ' and 'TStop4' | TTL input | (GND)                     |

| 007                | D2                 | TStop3   | TTL input Stop3                                         | TTL input | (10k $\Omega$ to GND)     |

| 008                | E1                 | StopDis3 | Disable inputs 'TStop5 ' and 'TStop6'                   | TTL input | (GND)                     |

| 009                | D3                 | StopDis4 | Disable or inputs 'TStop7 ' and 'TStop8'                | TTL input | (GND)                     |

| 010                | F1                 | Vddc     | Core supply voltage                                     |           | Vddc                      |

| 011                | E3                 | TStop4   | TTL input 'Stop4'                                       | TTL input | (10k $\Omega$ to GND)     |

| 012                | F2                 | Vssc     | Core GND                                                |           | GND                       |

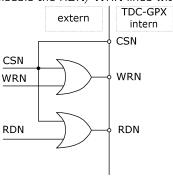

| 013                | G1                 | WRN      | Write (LOW active)                                      | TTL input |                           |

| 014                | F3                 | CSN      | Chip select (LOW active)                                | TTL input | (GND)                     |

| 015                | G2                 | RDN      | Read (LOW active)                                       | TTL input |                           |

| 016                | H1                 | Phase    | Phase output PLL                                        |           |                           |

| 017 | G3  | Vddo    | I/O supply voltage                        |                   | Vddo                   |

|-----|-----|---------|-------------------------------------------|-------------------|------------------------|

| 018 | H2  | Vsso    | I/O GND                                   |                   | GND                    |

| 019 | J1  | D0      | Data 0                                    | Bidirectional 4mA | 10kΩ to GND            |

| 020 | J2  | D1      | 1                                         | Bidirectional 4mA | 10kΩ to GND            |

| 021 | K1  | D2      | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 022 | K2  | D3      | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 023 | L1  | D4      | \                                         | Bidirectional 4mA | 10kΩ to GND            |

| 024 | L2  | D5      | \                                         | Bidirectional 4mA | 10kΩ to GND            |

| 025 | M1  | D6      | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 026 | N2  | D7      | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 027 | M2  | D8      | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 028 | N3  | D9      | `                                         | Bidirectional 4mA | 10kΩ to GND            |

| 029 | М3  | D10     | ,                                         | Bidirectional 4mA | 10kΩ to GND            |

| 030 | N4  | D11     | Data 11                                   | Bidirectional 4mA | 10kΩ to GND            |

| 031 | M4  | Vsso    | I/O GND                                   |                   | GND                    |

| 032 | N5  | D12     | Data 12                                   | Bidirectional 4mA | 10kΩ to GND            |

| 033 | L3  | D13     | `                                         | Bidirectional 4mA | 10kΩ to GND            |

| 034 | M5  | D14     | `                                         | Bidirectional 4mA | 10kΩ to GND            |

| 035 | N6  | D15     | `                                         | Bidirectional 4mA | 10kΩ to GND            |

| 036 | M6  | D16     | 1                                         | Bidirectional 4mA | 10kΩ to GND            |

| 037 | N7  | D17     | Data 17                                   | Bidirectional 4mA | 10kΩ to GND            |

| 038 | L5  | Vssc    | Core GND                                  |                   | GND                    |

| 039 | M7  | Vddc    | Core supply voltage                       |                   | Vddc                   |

| 040 | L6  | Vddo    | I/O supply voltage                        |                   | Vddo                   |

| 041 | M8  | D18     | Data 18                                   | Bidirectional 4mA | $10k\Omega$ to GND     |

| 042 | N9  | D19     | `                                         | Bidirectional 4mA | $10k\Omega$ to GND     |

| 043 | L7  | D20     | `                                         | Bidirectional 4mA | $10k\Omega$ to GND     |

| 044 | M9  | D21     | `                                         | Bidirectional 4mA | $10k\Omega$ to GND     |

| 045 | L8  | D22     | '                                         | Bidirectional 4mA | 10kΩ to GND            |

| 046 | M10 | D23     | Data 23                                   | Bidirectional 4mA | 10kΩ to GND            |

| 047 | L9  | Vsso    | I/O GND                                   |                   |                        |

| 048 | M11 | D24     | Data 24                                   | Bidirectional 4mA | 10kΩ to GND            |

| 049 | N12 | D25     | 1                                         | Bidirectional 4mA | 10kΩ to GND            |

| 050 | L10 | D26     | \                                         | Bidirectional 4mA | 10kΩ to GND            |

| 051 | M13 | D27     | Data 27                                   | Bidirectional 4mA | 10kΩ to GND            |

| 052 | N13 | EF1     | Interface FIFO 1 empty flag, active HIGH  | Output 4mA        |                        |

| 053 | L13 | EF2     | Interface FIFO 2 empty flag, active HIGH  | Output 4mA        |                        |

| 054 | L12 | Vddo    | I/O supply voltage                        |                   | Vddo                   |

| 055 | L11 | Vsso    | I/O GND                                   |                   | GND                    |

| 056 | K13 | RefClk  | Input reference clock                     | TTL input         |                        |

| 057 | K12 | LF1     | Interface FIFO 1 load flag, active HIGH * | Output 1mA        |                        |

| 058 | K11 | LF2     | Interface FIFO 2 load flag, active HIGH * | Output 1mA        |                        |

| 059 | J13 | IrFlag  | Interrupt flag, active HIGH               | Output 1mA        |                        |

| 060 | J12 | ErrFlag | Error flag, active HIGH                   | Output 1mA        |                        |

| 061 | H13 | Tstop8  | TTL input ,Stop8'                         | TTL input         | (10k $\Omega$ to GND)  |

| 062 | H12 | Vssc    | Core GND                                  |                   | GND                    |

| 063 | H11 | OEN     | Output enable, active LOW                 | TTL input         | (10k $\Omega$ to Vddo) |

\_

<sup>\*</sup> Valid only whileF13 it is not read

| 064 | G11 | Test       | acam test input, connect it to GND! | TTL input          | GND                   |

|-----|-----|------------|-------------------------------------|--------------------|-----------------------|

| 065 | F13 | Vsso       | I/O GND                             |                    | GND                   |

| 066 | F12 | Tstop7     | TTL input ,Stop7'                   | TTL input          | (10k $\Omega$ to GND) |

| 067 | F11 | PuResN     | Power-up reset, low active          | TTL input          |                       |

| 068 | E13 | Vssc       | Core GND                            |                    | GND                   |

| 069 | E12 | Vddc       | Core supply voltage                 |                    | Vddc                  |

| 070 | D12 | Tstop6     | TTL input 'Stop6'                   | TTL input          | (10k $\Omega$ to GND) |

| 071 | D13 | Adr3       | Address 3                           | TTL input          |                       |

| 072 | E11 | Adr2       | Address 2                           | TTL input          |                       |

| 073 | C13 | Adr1       | Address 1                           | TTL input          |                       |

| 074 | C12 | Adr0       | Address 0                           | TTL input          |                       |

| 075 | D11 | AluTrigger | External ALU trigger                | TTL input          | (10k $\Omega$ to GND) |

| 076 | C11 | Tstop5     | TTL input 'Stop5'                   | TTL input          | (10k $\Omega$ to GND) |

| 077 | A11 | Vddo       | I/O supply voltage                  |                    | Vddo                  |

| 078 | C10 | Vssc       | Core GND                            |                    | GND                   |

| 079 | B10 | Vddc       | Core supply voltage                 |                    | Vddc                  |

| 080 | C9  | Tstart     | TTL input 'Start'                   | TTL input          | (10k $\Omega$ to GND) |

| 081 | B9  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 082 | A9  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 083 | B8  | DStop2N    | Differential input 'Stop2', neg     | Differential input | (10k $\Omega$ to GND) |

| 084 | A8  | DStop2     | Differential input 'Stop2', pos     | Differential input | (10k $\Omega$ to GND) |

| 085 | C7  | Vsse       | LVPECL GND                          |                    | GND                   |

| 086 | B7  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 087 | A7  | Vddc-h     | Hardmacro supply voltage            |                    | Vddc-h                |

| 088 | C6  | Vddc-o     | Hardmacro supply voltage            |                    | Vddc-o                |

| 089 | B6  | Vssc-o     | Hardmacro GND                       |                    | GND                   |

| 090 | A6  | Vssc-h     | Hardmacro GND                       |                    | GND                   |

| 091 | C5  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 092 | B5  | DStartN    | Differential input 'Start' , neg    | Differential input | (10k $\Omega$ to GND) |

| 093 | A5  | DStart     | Differential input 'Start' , pos    | Differential input | (10k $\Omega$ to GND) |

| 094 | C4  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 095 | B4  | Vsse       | LVPECL GND                          |                    | GND                   |

| 096 | A4  | Dstop1N    | Differential input 'Stop1', neg     | Differential input | (10k $\Omega$ to GND) |

| 097 | В3  | Dstop1     | Differential input 'Stop1', pos     | Differential input | (10k $\Omega$ to GND) |

| 098 | А3  | Vdde       | LVPECL supply voltage               |                    | Vdde                  |

| 099 | B2  | TStop1     | TTL input 'Stop1'                   | TTL input          | (10k $\Omega$ to GND) |

| 100 | A2  | Vsso       | I/O GND                             |                    | GND                   |

|     |     |            |                                     |                    |                       |

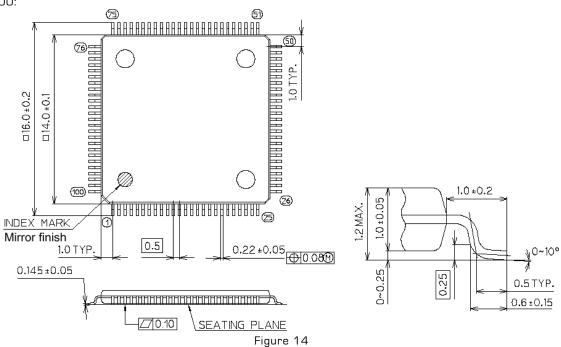

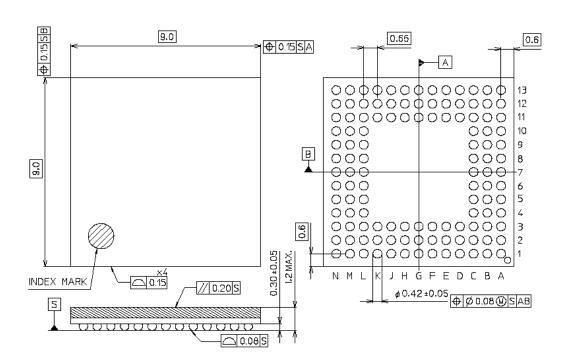

## 1.5 Package Drawings

TQFP100:

Sockets: E.g. Yamaichi IC149-100-025

TFBGA:

## 1.6 Power supply

## 1.6.1 Resolution adjust

In principle the high resolution of the TDC-GPX is derived from the internal gate propagation times. The gate propagation time depends upon voltage, temperature and the manufacturing process. Due to this dependency the resolution normally is not known and must be calculated via calibration measurements. In addition, the resolution is not stable, it sways with voltage and temperature. This does not apply using the resolution adjust mode for the TDC-GPX. In this mode the resolution of the TDC-GPX is adjusted quartz-accurately and absolutely temperature stable via Phase Locked Loop The phase locked loop (PLL) regulates the core voltage of the TDC-GPX so that the resolution is set exactly to the programmed value.

The BIN size is calculated as follows:

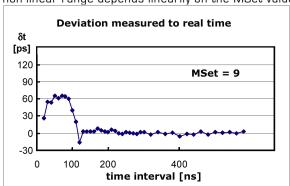

$$\begin{split} &BIN_{I-Mode} = \frac{T_{ref} \times 2^{refclkdiv}}{216 \times hsdiv} \\ &BIN_{G-Mode} = BIN_{I-Mode} \times \frac{1}{2} \\ &BIN_{R-Mode} = BIN_{I-Mode} \times \frac{1}{3} \\ &BIN_{M-Mode} = BIN_{R-Mode} \times \frac{1}{MSet + 1} \end{split}$$

Tref = 25ns (40 MHz reference clock) RefClkDiv, HSDiv → Register 7

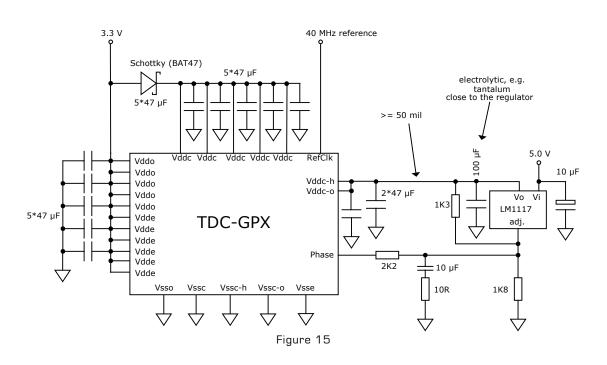

The adjustment range of the resolution can reach values from -40~% up to +9~% of the normal resolution at 3.3~V and  $25~^\circ\text{C}$ . If environmental conditions lead to very large adjustments the locked-state can be lost. Then the PLL changes to floating resolution until the conditions allow the PLL to lock again. Figure 15~shows the recommended external circuit for the regulation loop.

Note: See also application note ANO13.

Example:

RefClkDiv = 7 and HSDiv = 183 give the follow-

ing resolution:

I-Mode 80.9553 ps BIN G-Mode 40.4776 ps BIN R-Mode 26.9851 ps BIN

#### 1.6.2 Supply voltages

Although the TDC-GPX is a fully digital circuit, some analog measures affect the circuit. The reason is that the TDC is based on the internal analog measure 'propagation delay time' which is influenced by temperature and supply voltage. A good layout of the supply voltage is essential for good measurement results. It should be high capacitive and of low inductance.

There are several connections for power supply provided at the TDC-GPX:

Vddo - I/O supply voltage

Vddc - Core supply voltage

Vddc-h - Supply for the Hamac

Vddc-o - Supply for the ring oscillator

Vdde - Supply of LVPECL inputs

Vsso - I/O GND

Vssc - Core GND

Vssc-h - Hamac GND

Vssc-o - Ring oscillator GND

For a good stabilization we recommend the use of

$5 * 47 \mu F$ , one for each Vddc pin.

1 \* 47  $\mu$ F for Vddc-h.

1 \* 47  $\mu$ F for Vddc-o.

5 \* 47  $\mu$ F, total for Vddo and Vdde.

Recommended capacitors:

Taiyo-Yuden LMK325BJ476MM, 47µF, 1210

The supply voltage for the core should not be higher than the supply voltage of the I/O plus 0.6 V. Otherwise the signal flow could be disturbed.

All ground pins should be connected to a ground plane on the printed circuit board.

Vddc, Vddc-h and Vddc-o are floating and are supplied from the resolution adjust voltage regulator.

Vddo should be provided by a fixed voltage regulator to avoid disturbances caused by the inputs supply.

#### Power consumption

The current consumption is about 45 mA in R- and G-mode and 39mA in I-mode idle plus 5 mA per million events. At 1 million continuous events per second the junction temperature will increase to 17  $^{\circ}$ C above ambient.

The thermal resistance Rth j-a is 96K/W [still air] for the TQFP package and 105K/W for the TFBGA package. With available heatsinks it can be reduced to 35k/W [still air], due to a very small Rthj-c of the package.

The maximum junction temperature is Tj max =  $125 \, ^{\circ}\text{C}$ .

## 1.6.3 Design Rules

As shown in Figure 15 the supply voltage of the measuring unit, Vddc-o/h, is provided by an adjustable linear regulator. It is strongly recommended to use only LM317 or LM1117 regulators, because only for these regulators the circuit is tested and approved. Do not use low drop regulators because these regulators' reference refers to the output voltage and the regulation might be in conflict with the PLL regulation. The input voltage of the regulator should be  $\geq 5~\text{V}$  so that the maximum output voltage of the PLL regulation circuit is not limited by the voltage regulator's voltage drop of 1.2 V to 1.3 V.

Also for the other supply voltages, Vddc, Vddo & Vdde, linear regulators are recommended. Switched mode regulators will introduce a lot of noise to the measurement.

The width of the strip line between the regulator's output and the TDC-GPX power supply pins should be at least 50 mil.

For more detailed information concerning the PLL regulation circuit please refer to application note no. 13 at the end of this document.

## 1.7 Register settings

In depends on the operating mode whether bits are relevant or not. Especially the read data structure depends on the operating mode.

## 1.7.1 Write Registers

Service bits are for acam testing and security purposes only, Please use the recommended values. These registers can also be read back.

| Register ( | D: Adr = 0 |                                                     | - 1 | G | R | М |

|------------|------------|-----------------------------------------------------|-----|---|---|---|

| 0          | ROsc       | '1' = start ring oscillator                         | Х   | Х | Х | Х |

| 1          | RiseEnO    | '1' enable rising edge sensitivity on DStart input  |     | Х | Х | Х |

| 2          | FallEnO    | '1' enable falling edge sensitivity on DStart input |     | Х | Х | Х |

| 3          | RiseEn1    | '1' enable rising edge sensitivity on DStop1 input  |     | Х | Х | Х |

| 4          | FallEn1    | '1' enable falling edge sensitivity on DStop1 input |     | Х | Х | Х |

| 5          | RiseEn2    | '1' enable rising edge sensitivity on DStop2 input  |     | Х | Х | Х |

| 6          | FallEn2    | '1' enable falling edge sensitivity on DStop2 input |     | Х | Х | Х |

| 7 - 9      | HQSel      | Service bits, must be set to '001'                  | Х   | Х | Х | Х |

| 10 - 18    | TRiseEn    | '1' enables rising edges for the TTL inputs         | Х   |   |   |   |

|            |            | Bit 10 = TStart, Bit 11 = TStop1 Bit 18 = TStop8    |     |   |   |   |

| 19 - 27    | TFallEn    | '1' enables falling edges for the TTL inputs        | Х   |   |   |   |

|            |            | Bit 19 = TStart, Bit 20 = TStop1 Bit 27 = TStop8    |     |   |   |   |

| Register ' | 1: Adr = 1 |                                                            | G | R | M |

|------------|------------|------------------------------------------------------------|---|---|---|

| 0 - 3      | AdjO       | Channel adjustment bits channel O (Start)                  | Χ | Х | Х |

| 4 - 7      | Adj1       | Channel adjustment bits channel 1 (R-Mode = 2, G-Mode = 0) | Χ | Х | Х |

| 8 - 11     | Adj2       | Channel adjustment bits channel 2 (R-Mode = 6, G-Mode = 5) | Χ | Х | Х |

| 12 - 15    | Adj3       | Channel adjustment bits channel 3 (R-Mode = 0, G-Mode = 0) | Х | Х | Х |

| 16 - 19    | Adj4       | Channel adjustment bits channel 4 (R-Mode = 2, G-Mode = 5) | Χ | Х | Х |

| 20 - 23    | Adj5       | Channel adjustment bits channel 5 (R-Mode = 6, G-Mode = 0) | Х | Х | Х |

| 24 - 27    | Adj6       | Channel adjustment bits channel 6 (R-Mode = 0, G-Mode = 5) | Х | Х | Х |

Adjustment bits recommendation:

R-Mode: Adj1 = Adj4 = Adj7 = 2, Adj 2 = Adj 8 = 6, Adj5 = 6

G-Mode: Adj2 = Adj4 = Adj6 = Adj8 = 5.

| Register 2 | 2: Adr = 2 |                                                            | I | G | R | М |

|------------|------------|------------------------------------------------------------|---|---|---|---|

| 0          | G-Mode     | '1' = switch on G-Mode                                     |   | Х |   |   |

| 1          | I-Mode     | '1' = switch on I-Mode                                     | Х |   |   |   |

| 2          | R-Mode     | '1' = switch on R-Mode                                     |   |   | Х | Х |

| 3 - 11     | Disable    | '1' = disable channel                                      | Х | Х | Х | Х |

|            |            | Bit 3 = channel 0 (Start) Bit 11 = channel 8               |   |   |   |   |

| 12 - 15    | Adj7       | Channel adjustment bits channel 7 (R-Mode = 2, G-Mode = 0) |   | Х | Х | Χ |

| 16 - 19    | Adj8       | Channel adjustment bits channel 8 (R-Mode = 6, G-Mode = 5) |   | Х | Х | Х |

| 20 - 21    | DelRise1   | Service bits, set 'O'                                      |   | Х | Х |   |

| 22 - 23    | DelFall1   | Service bits, set 'O'                                      |   | Х | Х |   |

| 24 - 25    | DelRise2   | Service bits, set 'O'                                      |   | Х | Х |   |

| 26 - 27    | DelFall2   | Service bits, set 'O'                                      |   | Х | Х |   |

| Register 3 | 3: Adr = 3 |                                                                                                  | ı | G | R | М |

|------------|------------|--------------------------------------------------------------------------------------------------|---|---|---|---|

| 0 - 4      | MSet       | Setting resolution factors 1 to 31 in M-Mode                                                     |   |   |   | х |

| 5 - 6      | DelT1      | Service bits, set '0'                                                                            |   | Х | Х |   |

| 7 - 8      | DelT2      | Service bits, set '0'                                                                            |   | Х | Х |   |

| 9 - 10     | DelT3      | Service bits, set '0'                                                                            |   | Х | Х |   |

| 11 - 12    | DelT4      | Service bits, set 'O'                                                                            |   | Х | Х |   |

| 13 - 14    | DelT5      | Service bits, set '0'                                                                            |   | Х | Х |   |

| 15 - 16    | DelT6      | Service bits, set 'O'                                                                            |   | Х | Х |   |

| 17 - 18    | DelT7      | Service bits, set 'O'                                                                            |   | Х | Х |   |

| 19 - 20    | DelT8      | Service bits, set '0'                                                                            |   | Х | Х |   |

| 21 - 22    | RaSpeedO   | Service bits, set 'O'                                                                            |   | Х | Х |   |

| 23 - 24    | RaSpeed1   | Service bits, set 'O'                                                                            |   | Х | Х |   |

| 25 - 26    | RaSpeed2   | Service bits, set '0'                                                                            |   | Х | Х |   |

| 27         | GTest      | Switches TStart to DStart, TStop1 to DStop1 and TStop2 to DStop2 (TTL to ECL, testing in G-Mode) |   | Х | х | Х |

| Register 4: | Adr = 4      |                                                              | I | G | R | М |

|-------------|--------------|--------------------------------------------------------------|---|---|---|---|

| 0 - 7       | StartTimer   | defines repetition rate of internal Start in (N + 1)*Tref    | Х |   |   |   |

|             |              | recommended: 5 μs ( ( <u>199</u> + 1) * 25ns )               |   |   |   |   |

| 8           | Quiet        | '1' = Switch on Quiet Mode in G-, R- or M-Mode If Quiet is   |   | Х | Х | Х |

|             |              | set to '1', the ALU doesn't start automatically, but after a |   |   |   |   |

|             |              | rising edge at pin ALUTrigger or after writing '1' into Bit  |   |   |   |   |

|             |              | 'AluTrigSoft' (mandatory in M-Mode)                          |   |   |   |   |

| 9           | Mon          | Switch on M-Mode                                             |   |   |   | Х |

| 10 - 11     | RaSpeed3     | Pulse-pair timing adjust, typically set 'O'                  |   | Х | Х | Х |

| 12 - 13     | RaSpeed4     | Pulse-pair timing adjust, typically set 'O'                  |   | Х | Х | Х |

| 14 - 15     | RaSpeed5     | Pulse-pair timing adjust, typically set '0'                  |   | Х | Х | Х |

| 16 - 17     | RaSpeed6     | Pulse-pair timing adjust, typically set 'O'                  |   | Х | Х | Х |

| 18 - 19     | RaSpeed7     | Pulse-pair timing adjust, typically set 'O'                  |   | Х | Х | Х |

| 20 - 21     | RaSpeed8     | Pulse-pair timing adjust, typically set '0'                  |   | Х | Х | Х |

| 22          | MasterReset  | '1' = general reset excluding configuration registers        | Х | Х | Х | Х |

| 23          | PartialReset | '1' = general reset excluding configuration registers and    | Х | Х | Х | Х |

|             |              | Interface FIFO content                                       |   |   |   |   |

| 24          | AluTrigSoft  | Starts ALU in Quiet Mode                                     |   | Х | Х | Х |

| 25          | EFlagHiZN    | '1' = EF output pin is driving all the time                  | Х | Х | Х | Х |

| 26          | MTimerStart  | '1' = the internal MTimer is started with a Start pulse      | Х | Х | Х | Х |

| 27          | MTimerStop   | '1' = the internal MTimer is started with a Stop pulse       | Х | Х | Х | Х |

| Register 5: | Adr = 5        |                                                                | ı | G | R | М |

|-------------|----------------|----------------------------------------------------------------|---|---|---|---|

| 0 - 17      | StartOff1      | programmable internal Start-offset                             | Х | Х | Х | Х |

| 18 - 20     | ServiceMAdj    | Service bits, set "O"                                          |   |   |   | Х |

| 21          | StopDisStart   | Stop disable before a Start pulse                              | Х | Х | Х | Х |

| 22          | StartDisStart  | Start disable after a Start pulse                              |   | Х | Х | Х |

| 23          | MasterAluTrig  | Master reset by Alutrigger pin HIGH (only with no Quiet        | Х | х | х |   |

|             |                | Mode)                                                          |   |   |   |   |

| 24          | PartialAluTrig | Partial reset by Alutrigger pin HIGH (only with no Quiet Mode) | Х | Х | Х |   |

| 25          | MasterOenTrig  | Master reset by OEN pin LOW (only with OEN not used)           | Х | Х | Х | Х |

| 26          | PartialOenTrig | Partial reset by OEN pin LOW (only with OEN not used)          | Х | Х | Х | Х |

| 27          | StartRetrig    | Start retrigger                                                | Х | Х | Х |   |

| Register 6: | Adr = 6    |                                                              |   | G | R | М |

|-------------|------------|--------------------------------------------------------------|---|---|---|---|

| 0 - 7       | Fill       | Defines the level when the fill-level Flags LFx of the 2 in- | Х | Х | Х |   |

|             |            | terface FIFOs will be set.                                   |   |   |   |   |

| 8 - 25      | StartOff2  | programmable internal Start-offset (in G-Mode only)          |   | Х |   |   |

| 26          | InSelECL   | select ECL inputs for I-Mode DStop1 -> TStop1, TStop3,       | Х |   |   |   |

|             |            | TStop5, TStop7 DSTop2 -> TStop2, TStop4, TStop6,             |   |   |   |   |

|             |            | TStop8(single channels can be switched off using 'Dis-       |   |   |   |   |

|             |            | able'                                                        |   |   |   |   |

| 27          | PowerOnECL | '1' = Switch-on power for ECL-inputs                         | Х | Х | Х | Х |

When reading back register 6 the "Fill" bits 0 to 7 will be inverted.

| Register 7: Adr = 7 |           |                                                       |   | G | R | М |

|---------------------|-----------|-------------------------------------------------------|---|---|---|---|

| 0 - 7               | HSDiv     | High speed divider PLL                                | Х | Х | Х | Х |

| 8 - 10              | RefClkDiv | Reference clock divider PLL                           | Х | Х | Х | Х |

| 11                  | ResAdj    | Switch-on resolution adjust mode                      | Х | Х | Х | Х |

| 12                  | NegPhase  | Invert phase output of PLL                            | Х | Х | Х | Х |

| 13                  | Track     | cut regulation loop of PLL                            | Х | Х | Х | Х |

| 14                  | Service   | Service Bits, set 'O'                                 |   |   |   |   |

| 15 - 27             | MTimer    | Setting internal timer in multiples of Tref, 0 - 8191 | Х | Х | Х | Х |

| Register 14: Adr = 14 |                         |                                                 | - | G | R |   |

|-----------------------|-------------------------|-------------------------------------------------|---|---|---|---|

| 0 - 3                 | O - 3 Service Write "O" |                                                 |   |   | Χ | Χ |

| 4                     | 16BitMode               | '1' switches on the 16 Bit mode of the data bus | Х | Х | Х | Х |

| 5 - 27                | Service                 | Write "0"                                       | Χ | Χ | Χ | Χ |

After 16 Bit mode is set all further read/write commands have to be done in pairs of 16 Bit.

## 1.7.2 Read registers

## I-Mode

| Register 8: | Register 8: Adr = 8 |                                                           |  |  |  |

|-------------|---------------------|-----------------------------------------------------------|--|--|--|

| 0 - 16      | IFIFO1              | Time interval data from Interface FIFO1, Hit = Stop-Start |  |  |  |

| 17          | Slope1              | Slope of this hit                                         |  |  |  |

| 18 - 25     | Start#1             | Start number of this hit                                  |  |  |  |

| 26 - 27     | ChaCode1            | Channel code of this hit                                  |  |  |  |

| Register 9: | Register 9: Adr = 9 |                                                           |  |  |

|-------------|---------------------|-----------------------------------------------------------|--|--|

| 0 - 16      | IFIFO2              | Time interval data from Interface FIFO2, Hit = Stop-Start |  |  |

| 17          | Slope2              | Slope of this hit                                         |  |  |

| 18 - 25     | Start#2             | Start number of this hit                                  |  |  |

| 26 - 27     | ChaCode2            | Channel code of this hit                                  |  |  |

| Register 10 | Register 10: Adr = 10 |                                                               |  |  |  |

|-------------|-----------------------|---------------------------------------------------------------|--|--|--|

| 0 - 16      | Start01               | Time interval between external start and first internal start |  |  |  |

| 17 - 27     | -                     | not used                                                      |  |  |  |

## G-Mode

| Register 8: | Register 8: Adr = 8 |                                                           |  |  |  |

|-------------|---------------------|-----------------------------------------------------------|--|--|--|

| 0 - 21      | IFIFO1              | Time interval data from Interface FIFO1, Hit = Stop-Start |  |  |  |

| 22          | Slope1              | O = falling edge, 1 = rising edge                         |  |  |  |

| 23 - 27     | -                   | not used                                                  |  |  |  |

| Register 9: | Register 9: Adr = 9 |                                                           |  |  |  |

|-------------|---------------------|-----------------------------------------------------------|--|--|--|

| 0 - 21      | IFIFO2              | Time interval data from Interface FIFO2, Hit = Stop-Start |  |  |  |

| 22          | Slope2              | O = falling edge, 1 = rising edge                         |  |  |  |

| 23 - 27     | -                   | not used                                                  |  |  |  |

| Register 10: Adr = 10 |          |          |  |  |

|-----------------------|----------|----------|--|--|

| 0 - 15                | not used |          |  |  |

| 16 - 27               | -        | not used |  |  |

## R-Mode & M-Mode

| Register 8: | Register 8: Adr = 8 |                                                           |  |  |  |

|-------------|---------------------|-----------------------------------------------------------|--|--|--|

| 0 - 22      | IFIFO1              | Time interval data from Interface FIFO1, Hit = Stop-Start |  |  |  |

| 23 - 27     | -                   | not used                                                  |  |  |  |

| Register 9: Adr = 9 |                                                                             |          |  |  |

|---------------------|-----------------------------------------------------------------------------|----------|--|--|

| 0 - 22              | 0 - 22   IFIFO2   Time interval data from Interface FIFO2, Hit = Stop-Start |          |  |  |

| 23 - 27             | -                                                                           | not used |  |  |

| Register | Register 10: Adr = 10 |          |  |  |  |

|----------|-----------------------|----------|--|--|--|

| 0 - 15   | -                     | not used |  |  |  |

| 16 - 27  | -                     | not used |  |  |  |

## 1.7.3 Read/Write registers

| Register 11 | Register 11: Adr = 11 |                                                          |            |  |  |

|-------------|-----------------------|----------------------------------------------------------|------------|--|--|

| 0 - 7       | StopCounter0          | # of hits on DStop1,                                     | read only  |  |  |

|             |                       | I-Mode: not available                                    |            |  |  |

|             |                       | G-Mode: counting falling edge                            |            |  |  |

|             |                       | R-Mode: counting rising edge                             |            |  |  |

| 8 - 15      | StopCounter1          | # of hits on DStop2,                                     | read only  |  |  |

|             |                       | I-Mode: not available                                    |            |  |  |

|             |                       | G-Mode: counting falling edge                            |            |  |  |

|             |                       | R-Mode: counting rising edge                             |            |  |  |

| 16 - 23     | HFifoErrU             | '1' unmasks full flags of Hit FIFOs to ErrFlag pin       | read/write |  |  |

| 24 - 25     | IFifoErrU             | '1' unmasks full flags of Interface FIFOs to ErrFlag pin | read/write |  |  |

| 26          | NotLockErrU           | '1' unmasks 'PLL not locked' to ErrFlag pin              | read/write |  |  |

| Register 12 | 2: Adr = 12 |                                                           |            |

|-------------|-------------|-----------------------------------------------------------|------------|

| 0 - 7       | HFifoFull   | Full flags of Hit FIFOs                                   | read only  |

| 8 - 9       | IFifoFull   | Full flags of Interface FIFOs                             | read only  |

| 10          | NotLocked   | 'PLL not locked' flag                                     | read only  |

| 11          | HFifoE      | Falg indicating that all Hit FIFOs are empty              | read only  |

| 12          | TimerFlag   | Flag indicating end of MTimer                             | read only  |

| 13 - 20     | HFifoIntU   | '1' unmasks full flags of Hit FIFOs to IntFlag pin        | read/write |

| 21 - 22     | IFifoIntU   | '1' unmasks full flags of Interface FIFOs to IntFlag pin  | read/write |

| 23          | NotLockIntU | '1' unmasks 'PLL not locked' to IntFlag pin               | read/write |

| 24          | HFifioEU    | '1' unmasks 'All Hit FIFOs empty' to IntFlag pin          | read/write |

| 25          | TimerFlagU  | '1' unmasks end of MTimer to IntFlag pin                  | read/write |

| 26          | Start#U     | '1' unmasks highest bit of Start# (I-Mode) to IntFlag pin | read/write |

| 27          | Service     | Set to "O"                                                | read/write |

HFifoFull and IFifoFull will be set back to "O" when reading register 12. They are re-activated by a master reset or a partial reset.

## 2 I-Mode

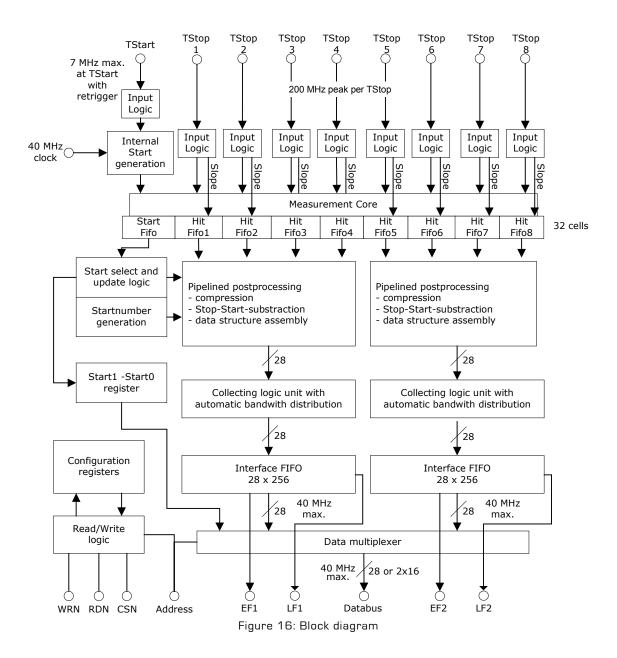

## 2.1 Block diagram I-Mode

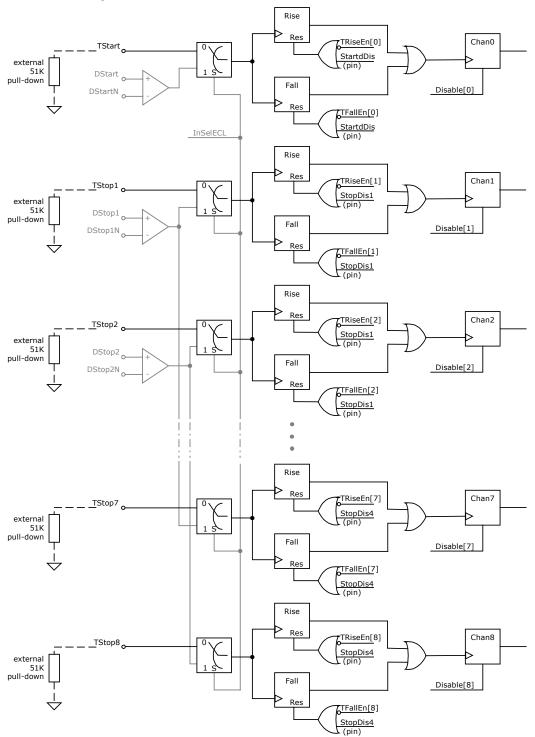

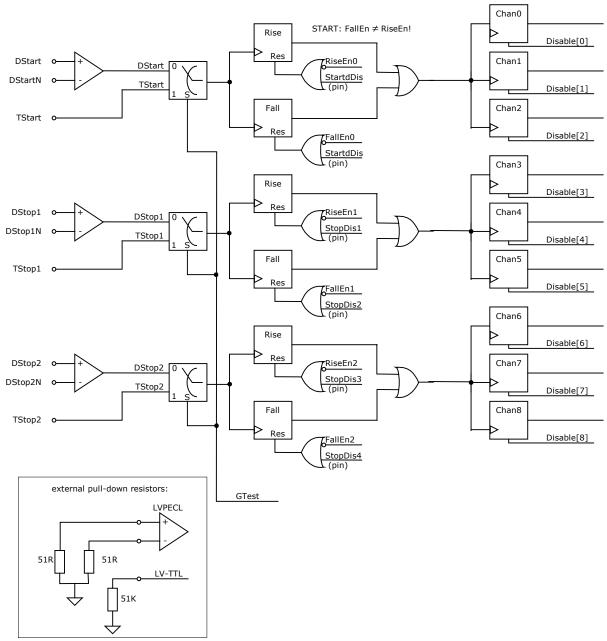

## 2.2 Input circuitry I-Mode

Figure 17: Input circuitry

## 2.3 I-Mode Basics

In this mode TDC-GPX offers

- 8 stop channels referring to 1 start channel,

- Each of typ. 81 ps resolution

- 5.5 ns pulse-pair resolution

- Start-retrigger up to 7 MHz

- Unlimited measuring range with internal start retrigger

- All inputs of LVTTL type

- Selectable rising/falling edge sensitivity for all channels

- Several disable possibilities for all channels

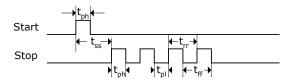

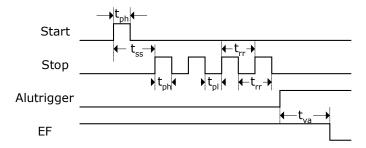

Figure 18: Measurement timings

| Par.            | Time (Condition) |            | Description          |

|-----------------|------------------|------------|----------------------|

|                 | Min.             | Max.       |                      |

| t <sub>ph</sub> | 1.5 ns           |            | Positive pulse width |

| t <sub>pl</sub> | 1.5 ns           |            | Negative pulse width |

| tss             | 0 ns min         | 9.4 µs     | Start to Stop        |

|                 | * * 5.2 ns       | *unlimited |                      |

| trr,            | 5.5 ns typ.      |            | edge to edge         |

| tff             | 6.9 ns max.*     |            | # @ 87 ps resolution |

\*with int. start retrigger \*\*with StopDisStart = 1

#### Input circuitry

The detailed input structure is shown in Figure 17: Input circuitry. Each input separately can be set to be sensitive to rising or falling edge. This is done in registerO, TRiseEn[8...O] and TFallEn[8...O]. The LSB stands for the TStart input, the MSB TStop8 input. A zero in the channel bit for TRiseEn and TfallEn at the same time disables the channel.

All inputs can be disabled by hardware, the stop inputs in pairs (pin 'StopDis1' disables inputs TStop1 and TStop2, etc.). They also can be disabled by Software setting the 'Disable' bits in register 2. The TDC-GPX offers the possibility to disable the Stop inputs automatically until a Start is coming in. This is set by StopDisStart = '1' in register 5.

## Start Retrigger

After an initial start event, the TDC-GPX can generate its own internal starts. This is controlled by the parameter "StartTimer" in register 4. The start retrigger rate may not exceed 7 MHz.

#### Single Start

StartTimer = 0 switches off the internal Start generation. In this mode the measuring range is limited to  $2^{17}$  BIN  $\approx 10.6~\mu s$  (@ BIN = 81 ps). Further pulses at TStart will be ignored.

#### Internal Start Retrigger

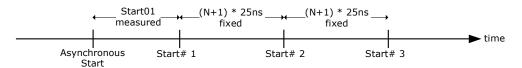

The period of the start repetition is programmable in multiples of the 40 MHz reference clock between [4+1] and [255+1] x 25ns (Register 4: Start-Timer[7...0]).

The time interval between the initial, external start and the first internal one will vary. It is therefore measured and stored as 'StartO1' in register 10. It can be read out from this register as a 17 Bit integer in multiples of BIN

The time intervals between following starts are fixed and referred to as  $(N + 1) \times Tref$ . Additionally, there is an 8 Bit counter for the start number (Start#). The start number is added to the output data.

A further option is to feed the highest bit of the Start counter to the IrFlag output pin by setting register 11, Bit 26 Start#U to one. With this signal the intenal start number counter can externally be extended to any size.

The internal start retrigger allows an **unlimited measuring range** for the TDC-GPX.

## External Start Retrigger

A further option is to retrigger the Start externally. This option is activated by setting StartTimer = 1 (Reg 4) and StartRetrig = 1 (Reg 5). The further behavior is the same as for the internal start retrigger. The maximum retrigger frequency is typically 7 MHz. The time interval between two Starts is measured and stored in the "StartO1" register. This value is reasonable only if the delay between two Start pulses does not exceed the measuring range of  $2^{17}$  BIN  $\approx 10.6~\mu s$ .

Figure 19

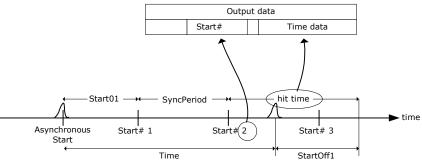

#### Start-Offset

For several reasons a mathematical offset is added to the stop time. One reason is to allow handling Start-Stop intervals down to O and even less. This 'StartOff1' is set in register 5 in multiples of BIN and it is 18 Bit wide. Internally the start offset is added to the time measurement result and has to be subtracted from the value read from the TDC. The other reason is to allo the ALU to look "into the past" without handling negative values (which the ALU could not do).

Figure 20

The real time interval Start to Stop is calculated from the output data as (Start # >0):

Time = (hittime - StartOff1 + Start01) \* resolution + (Start# - 1) \* (StartTimer +1) \* Tref

## Adjusting the Start-Offset

The Start-Offset register of the TDC-GPX allows the compensation for the offset due to the different internal delays. It allows to do measurements down to 0 ns time intervals between Start and Stop. The correct setting should be done by experiment.

Procedure for single start applications:

- 1. Set StartOff1 = 0

- 2. Apply Start and Stop signals with a short delay [e.g. 12ns]

- 3. Step down the interval and look at the output data. They are getting smaller and smaller until you pass the internal Start time stamp. The output data then jumps to a very high value.

- Take the time interval t<sub>cross</sub> (from your generator) where this happens

- 5. Calculate StartOff1 = t<sub>cross</sub> / BIN and write this value into register 5, StartOff1. In case you expect negative values add an additional amount X to StartOff1 and substract this value later on from your output data

With <u>start retrigger</u> the value StartOff1 should be set to

$$StartOff1 = 2,000 (\approx 162 ns).$$

The reason is that the ALU is internally stopped for about 50 ns during a start retrigger to add the new start time stamp. If there is a hit on each channel during this period the ALU will need

$4 \times 25 \text{ ns} + 50 \text{ ns} = 150 \text{ ns}$  to transfer those data to the IFIFO. The ALU cannot handle negative values.

Therefore the start offset is added so that the ALU can handle the data being collected during the break. In case the input data rate is higher (bursts) it will be necessary to increase also the offset value, e.g. to 10,000.

The start retrigger adds some indeterminacy – due to the 25ns reference – to whether a stop refers to the old start or the new one. This is not an uncertainty. Each time stamp that is negative after offset substraction can be remapped to the old start by adding the

start period and reducing the start number by 1.

## StopDisStart & StartDisStop

By default the Start and Stop inputs of the TDC-GPX are open immediately after a reset.

The consequence for the Stop channels is that even hits coming before a Start pulse will be measured. The bit StopDisStart in register 5 disables the Stop channels until there is a Start pulse. A consequence is that there is a minimum delay of 7 ns after the Start before hits are accepted on the Stop channels.

With single-start and internal start-retrigger only the first Start pulse is used for the measurement. In cases where more than one Start pulse is expected this might cause an overflow of the Hit FIFO of the Start channel. This will produce garbage data. There we recommend setting the StartDisStart bit in register 5. A '1' disables the Start channel after the first Start pulse.

## Internal Data Processing

The raw values of the stop events are stored in 32-stage Hit FIFOs. One bit is added indicating the slope of the signal. This Hit FIFO can be filled with data at a peak rate of 182 MHz.

The following pipelined post-processing unit is responsible for compression, Start selection, correct Stop-Start subtraction and adding the start number to the output data. Subsequently a collection unit transfers

the data to the Interface FIFO, which is 256 stages deep. This is done with respect to automatic bandwidth distribution. If a hit from one channel has been processed, the neighbored channel gets highest priority for next operation. If there is no hit on the next, the next sequential gets priority and so on. The maximum rate for transfer into the Interface FIFO is 40 MHz. So if there are hits on all channels equally distributed, the maximum rate per channel is 10 MHz. If there are hits on only one channel, this channel has 40 MHz maximum rate.

Finally a data multiplexer adds data from both Interface FIFOs to the data bus. The data bus is 28 Bits wide and capable of 40 MHz transfer rate. The data bus can be switched to 16 Bit width writing 0x0000010 into address 14. A LOW at pin 'Output enable' forces the bidirectional bus drivers to permanent output state. This is helpful for fast data read out routines.

Each Interface FIFO has an empty flag (EF) and a load-level flag (LF). All flags are HIGH active. At low data rates it is recommended to check the EF to see whether there are data available for read out. It is not allowed to read from an empty Interface FIFO. The LF is helpful at high data rates. The load level threshold can be set in 'Fill' in register 6 and is the same for both FIFOs. As soon as the set number of data is available this can be read from the FIFO as a block without the need of checking the EF.

Note: the load-level flags are not synchronized. The load-level flag for a FIFO is valid only if it is <u>not</u> read from this FIFO. Otherwise there might be spikes.

#### 2.4 Data structure

The output data are integers with a BIN width defined by the setting of the resolution adjust unit [1.6.1 Resolution adjust],

$$BIN = \frac{T_{ref} \times 2^{refclkdiv}}{216 \times hsdiv}$$

| Bits    | Bits    | Bit   | Bits               |

|---------|---------|-------|--------------------|

| 2726    | 2518    | 17    | 160                |

| Channel | Start#  | Slope | Time interval data |

| code    | = Start |       | Hit = Stop-Start   |

|         | number  |       |                    |

The time interval is calculated (externally) as: If Start# is 0:

$$\label{eq:Time of StartOff1} Time = 1 \ BIN(ps) * \{Hit - StartOff1\}$$

If Start# > 0:

#### 2.5 Reset

There are 3 ways of resetting the device:

- Power-up reset: a low signal at pin PURESN resets the whole chip.

- Master-Reset: this command resets everything except the configuration registers. It can be done by software writing to register 4. When Master-AluTrig in register 5 is set to '1' it can be done also by a HIGH at the Alutrigger input pin.

- Partial-Reset: this command resets everything except the configuration registers and the Interface FIFOs. It can be done by software writing to register 4. When PartialAluTrig in register 5 is set to '1' it can be done also by a HIGH at the Alutrigger input pin.

After a Power-on reset and a Master reset it takes 40 ns before the Start and Stop inputs accept data. After a Partial reset it takes 75 ns before the Start and Stop inputs accept data.

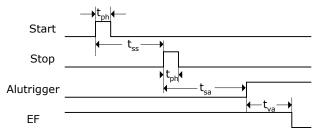

#### 2.6 MTimer

There is an internal timer available for internal use. The main application will be setting a dedicated time interval between 25ns and 204.7  $\mu s$  after which the interrupt flag is set. The period is set in 'MTimer', register 7, in multiples of Tref. The maximum delay is 8191 \* Tref = 204.7  $\mu s$ . The timer can be started by a Stop and/or Start signal. This is set in 'MTimerStart' and 'MTimerStop', register 4. Setting Bit 'TimerFlag', register 12, the interrupt flag is set when the timer stops.

## 2.7 Interrupt Flag

The user can select on which event(s) the interrupt flag is set.

The selection is done in register 12, Bits 13 to 25, by unmasking the dedicated bits. They are combined by an Or-Gate to the interrupt flag.

Selectable events are

- Hit FIFOs 1, 2 ...or/and 8 are full

- Interface FIFOs 1 or/and 2 are full

- PLL not locked

- All Hit FIFOs empty

- End of Mtimer

## 2.8 Error Flag

The user can select on which event(s) the error flag is set.

The selection is done in register 11, Bits 16 to 26, by unmasking the dedicated bits. They are combined by an Or-Gate to the error flag.

Selectable events are

- Hit FIFOs 1, 2 ...or/and 8 are full

- Interface FIFOs 1, 2 ...or/and 8 are full

- PLL not locked

## 2.9 Differential Inputs

It is possible to use the differential inputs also in I-Mode. Setting register 6, InSelECL= '1' switches the measurement channels to the two available differential inputs.

The power for the differential inputs has to be switched on separately by setting register 6, Power-OnECL = '1'.

## 2.10 I-Mode Timing & Resolution

The delay parameters vary with voltage, temperature and process tolerance. The following table lists the derating factors.

| Derating by | Minimal        | Maximal        |

|-------------|----------------|----------------|

| Voltage     | 0.91 at 3.6V   | 1.2 at 2.85V   |

| Temperature | 0.889 at -40°C | 1.17 at +125°C |

| Process     | 0.74 at BC     | 1.31 at WC     |

With the stabilization of the resolution by the resolution adjust mode, the voltage of the core decreases with decreasing temperature, and increases with increasing temperature. The setting should be done in a way that at maximum operating temperature the maximum core voltage is reached, and that minimum core voltage is reached at minimum operating temperature. With this method you get two limits:

Best case process, deepest temperature, lowest voltage:  $0.74 \times 0.889 \times 1.2 = 0.789$ Worst case process, highest temperature, highest voltage:  $1.31 \times 1.17 \times 0.91 = 1.394$

With a typical resolution of 81 ps (typ. process, 25°C, 3.3 V) you get two limits for the resolution:

|            | Best  | Worst  |

|------------|-------|--------|

| Resolution | 64 ps | 113 ps |

The BIN or LSB width is defined by the setting of the resolution adjust unit (1.6.1 Resolution adjust),

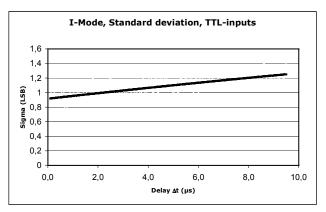

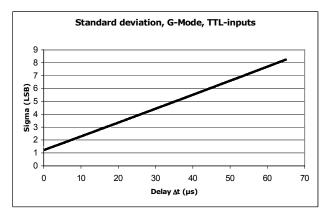

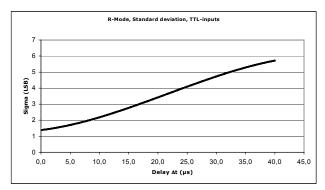

The standard deviation [1  $\sigma$ ] of the result is typically 0.9 LSB + 2,5ps \*  $\Delta t/\mu s$ .

Figure 21

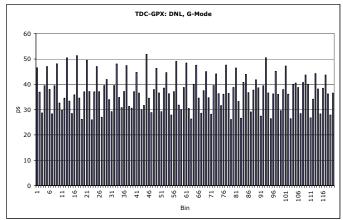

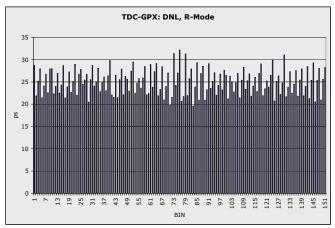

#### DNL

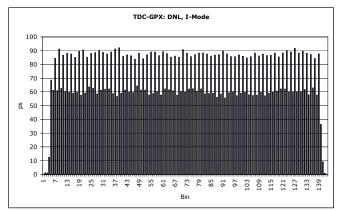

the TDC-GPX shows a moderate differential non-linearity (DNL) because internal propagation delays were used for the time measurement and because those delays are different for rising and falling edges. But the variation from channel to channel is strongly systematic. The following diagram shows the DNL data at a resolution of 74 ps:

Figure 22: DNL

#### INL

The integral non-linearity describes the deviation over the full measuring range. The INL of the TDC-GPX for a single Start-Stop measurement with a delay > 6 ns is below our measurement capability and can be neglected. In the close-up region below 6 ns the deviation is about 100 ps.

## 2.11 Measurement Flow

In the following we show two typical examples of register settings and measurement flow in I-Mode.

## 2.11.1 Single measurement

Task:

Measuring 8 channels within a window of 2 µs from Start.

```

//***** I-Mode, Stops against single Start *******

PuResN=Low;

// Power-up reset

PuResN=High;

StopDis1 = High;

// Disable inputs

StopDis2 = High;

StopDis3 = High;

StopDis4 = High;

// write configuration registers:

_oupd( 0,0x007FC81);

// Rising edges, Start ringoscil.

_oupd( 1,0x0000000);

_oupd( 2,0x0000002);

// I-Mode

_oupd( 3,0x0000000);

_oupd( 4,0x6000000);

// Mtimes trig. by Start, EFlagHiZN

//StopDisStart, StartDisStart, StartOff1 = 100ns, MasterAluTrig

_oupd( 5,0x0E004DA);

_oupd( 6,0x0000000);

_oupd( 7,0x0281FB4);

// Res = 82.3045ps

_oupd(11,0x7FF0000);

// Any error -> ErrFlag

_oupd(12,0x2000000);

// Mtimer -> IrFlag

_oupd(14,0x0000000);

_oupd( 4,0x6400000);

// Master reset

// Enable inputs

StopDis1 = Low;

StopDis2 = Low;

StopDis3 = Low;

StopDis4 = Low;

do

while(IrFlag=Low);

// Check interrupt flag

while((EF1=Low)or(EF2=Low))

// Check empty flag

// Data on IFIF01?

if (EF1=Low)

{

data = _inpd(8);

Chan = (data & 0xC000000)>>26 + 1;

// Read IFIF01

// Get channel#

Time = (data & 0x1FFFF);

// Get time Stop-Start

Printf(Chan, time);

if (EF2=Low)

// Data on IFIFO2?

{

data = _inpd(9);

Chan = ((data & 0xC000000)>>26) + 5;

// Read IFIFO2

// Get channel#

Time = (data & 0x1FFFF);

// Get time Stop-Start

Printf(Chan, time);

}

}

Alutrigger = High;

// Master reset

Alutrigger = Low;

} while(!quit)

```

## 2.11.2 Continous Measurement

Task: Typical application fluorescence spectroscopy.

Measuring a continous signal stream using the internal start-retrigger.

```

//***** I-Mode, endless measurement range with internal start retrigger ********

PuResN=Low;

// Power-up reset

PuResN=High;

// Disable inputs

StopDis1 = High;

StopDis2 = High;

StopDis3 = High;

StopDis4 = High;

// write configuration registers:

_oupd( 0,0x007FC81);

// Rising edges, Start ringoscil.

_oupd( 1,0x0000000);

_oupd( 2,0x0000002);

// I-Mode

_oupd( 3,0x0000000);

// StartTimer = 39 -> period = 1µs, EFlagHiZN

_oupd( 4,0x2000027);

_oupd( 5,0x02004DA);

// StopDisStart, StartOff1 = 100ns

_oupd( 6,0x000000);

_oupd( 7,0x0281FB4);

// Res = 82.3045ps

_oupd(11,0x7FF0000);

// Any error -> ErrFlag

_oupd(12,0x4000000);

// Start# overflow to IrFlag

_oupd(14,0x0000000);

// Master reset

_oupd( 4,0x6400027);

StopDis1 = Low;

// Enable inputs

StopDis2 = Low;

StopDis3 = Low;

StopDis4 = Low;

Wait(1µs);

// Wait until Start01 is available from register 10

// read Sta01 = interval first int. Start - ext. Start

Sta01 = -inpd(10) \& 0xFFFF

do

if (EF1=Low)

// Data on IFIFO1?

data = inpd(8);