# LTDC-X3

2-Channel LiDAR Time-to-Digital Converter

#### LTDC-X3 datasheet

Revision: E

Release Date: 2024-11-07

Document Status: Preliminary

LTDC-X3 is a high-performance 2-channel time-to-digital converter specifically designed for single-beam LIDAR systems. It has a separate START channel, two STOP channels, measures up to 4 pulses on rising and/or falling edges, has a pulse-pair resolution as low as 5 ns, a typical rms resolution of 30 ps and a range up to 2.4 µs. It integrates a start pulse generator for generation of trigger signals to an external laser diode driver.

Equipped with a guad SPI interface, the data rate can be as high as 50MHz / 200MBPS.

It comes in a QFN32 package and works in the industrial temperature range.

## **Key Benefits**

- Simple data post-processing thanks to calibrated results

- Optimized for LiDAR applications

- High efficiency thanks high sample rate

- Compact design thanks to small package and low number of external components

- Reduced cooling thanks to low power consumption

# **Key Features**

- Two TDC stop channels, one separate TDC start channel

- Pulse measurements on rising and falling edge

- Minimal pulse width 2.5ns

- Minimal pulse-to-pulse spacing 5ns (combined channels)

- Stop measurement of up to 4 pulses on rising and falling edge

- Stop mask window

- Maximal measuring range 2.4us

- Typical rms Resolution 30 ps

- Stop input Comparator compatible with LVDS

- 50MHz/200MBPS Quad SPI interface

- Start pulse generator including configurable phase noise

# **Applications**

- Robotics LiDAR

- Range finders

- Door scanners

- Safety scanners

## **Properties**

- Supply voltage 3.3 V

- Temperature range -40°C to +125°C

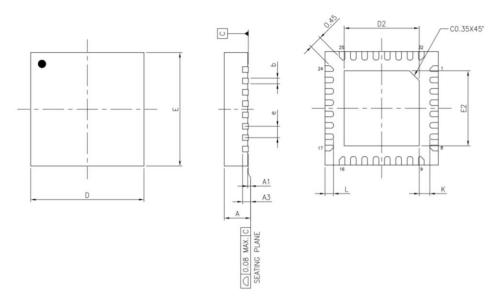

- QFN32 package

# **Content Guide**

| Κe | y I                   | Benefits                                    | . 2                  |  |  |  |  |

|----|-----------------------|---------------------------------------------|----------------------|--|--|--|--|

| Κe | y I                   | Features                                    | . 2                  |  |  |  |  |

| Αŗ | pplications           |                                             |                      |  |  |  |  |

| Pr | ор                    | erties                                      | . 2                  |  |  |  |  |

| Cc | ont                   | ent Guide                                   | . 3                  |  |  |  |  |

| 1  | ı                     | Block diagram                               | . 4                  |  |  |  |  |

| 2  | ı                     | Pin assignment                              | . 5                  |  |  |  |  |

| 3  | ,                     | Absolute maximum ratings                    | . 7                  |  |  |  |  |

| 4  |                       | Recommended Operating Conditions            |                      |  |  |  |  |

| 5  | 5.<br>5.              |                                             | 10                   |  |  |  |  |

| 6  | 6.:<br>6.:            | 3                                           | 13                   |  |  |  |  |

| 7  | 7<br>7<br>7<br>7<br>7 | Start-up Sequence                           | 28<br>31<br>31<br>35 |  |  |  |  |

| 8  | 8.2<br>8.2<br>8.2     | Configuration Example                       | 49<br>49<br>49       |  |  |  |  |

| 9  |                       | Soldering information                       |                      |  |  |  |  |

| 10 | )                     | Package drawings & markings                 | 51                   |  |  |  |  |

|    |                       | Ordering information                        |                      |  |  |  |  |

| 12 | 2 1                   | RoHS Compliance & ScioSense Green Statement | 53                   |  |  |  |  |

| 13 | 3 (                   | Copyrights & Disclaimer                     | 53                   |  |  |  |  |

| 14 | <b>4</b> I            | Document status                             | 54                   |  |  |  |  |

| 15 | 5 1                   | Revision information                        | 54                   |  |  |  |  |

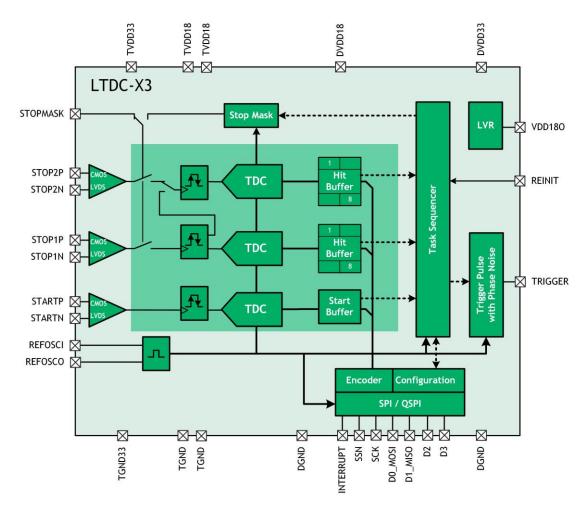

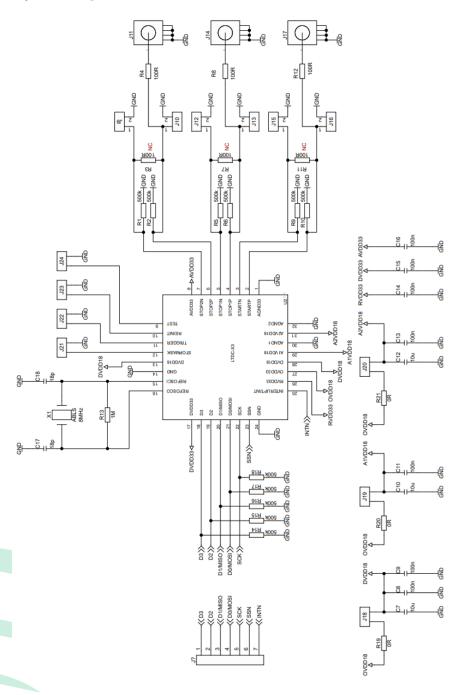

# 1 Block diagram

The functional blocks of this device are shown below.

Figure 1: Functional Blocks

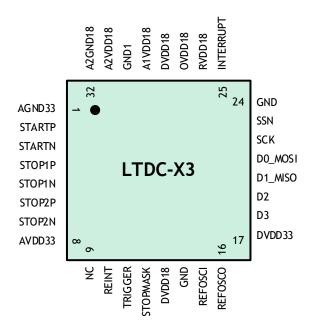

# 2 Pin assignment

Figure 2: Pin diagram

Table 1: Pin description

| Pins | Pin Name | Pin Type¹ | Description                                   | If not used |

|------|----------|-----------|-----------------------------------------------|-------------|

| 1    | AGND33   | S         | Ground supply for time front-end              |             |

| 2    | STARTP   | LVDSP_DI  | Positive LVDS / CMOS start input              |             |

| 3    | STARTN   | LVDSN     | Negative LVDS start input                     |             |

| 4    | STOP1P   | LVDSP_DI  | Positive LVDS / CMOS input for stop channel 1 |             |

| 5    | STOP1N   | LVDSN     | Negative LVDS input for stop channel 1        |             |

| 6    | STOP2P   | LVDSP_DI  | Positive LVDS / CMOS input for stop channel 2 |             |

| 7    | STOP2N   | LVDSN     | Negative LVDS input for stop channel 2        |             |

| 8    | AVDD33   | S         | 3.3V positive supply for time front-end       |             |

| 9    | NC       | 10        | Not connected                                 | GND         |

| 10   | REINIT   | DI_PD     | Re-init TDC command                           |             |

| 11   | TRIGGER  | DO        | Trigger pulses with phase noise               |             |

| 12   | STOPMASK | DI_PD     | Input signal to mask the stop inputs          |             |

<sup>&</sup>lt;sup>1</sup> S supply pad, AIO analog I/O, DI digital input, LVDSP\_DI LVDS positive input / CMOS digital input, LVDSNLVDS negative input, DI\_PU digital input with pull-up, DI\_PD digital input with pull-down, DI\_PU\_STdigital Schmitt trigger input with pull-up, DI\_PD\_ST digital Schmitt trigger input with pull-down, DIO\_PU I/O with pull-up, DIO\_PD digital I/O with pull-down, DIO\_T digital I/O / tristate, DO digital output, DO\_PD digital output with pull-down, DO\_ODPU digital output open drain with pull-up, DO\_ODPD digital output open drain with pull-down

| 13 | DVDD18    | S     | 1.8V supply for digital and IO units                   |

|----|-----------|-------|--------------------------------------------------------|

| 14 | GND       | S     | Ground for digital blocks and IO units                 |

| 15 | REFOSCI   | AIO   | Input for quartz as reference clock                    |

| 16 | REFOSCO   | AIO   | Output for quartz as reference clock                   |

| 17 | DVDD33    | S     | 3.3V supply for digital and IO units                   |

| 18 | D3        | DIO_T | QSPI/SPI Data Output 3                                 |

| 19 | D2        | DIO_T | QSPI/SPI Data Output 2                                 |

| 20 | D1        | DIO_T | QSPI/SPI Data Output 1 / Master Input Slave Output     |

| 21 | D0        | DIO_T | QSPI/SPI Data Output 0 / Master Output Slave Input     |

| 22 | SCK       | DI    | QSPI/SPI clock                                         |

| 23 | SSN       | DI_PU | QSPI/SPI chip select                                   |

| 24 | GND       | S     | Ground for digital blocks and IO units                 |

| 25 | INTERRUPT | DO    | Interrupt output                                       |

| 26 | RVDD33    | S     | 3.3V positive supply for LDO                           |

| 27 | OVDD18    | S     | 1.8V supply for digital and IO units, regulator output |

| 28 | DVDD18    | S     | 1.8V supply for digital and IO units                   |

| 29 | A1VDD18   | S     | 1.8V supply for analog block                           |

| 30 | GND1      | S     | Ground for analog 1.8V block                           |

| 31 | A2VDD18   | S     | 1.8V supply for analog block                           |

| 32 | A2GND18   | S     | Ground for analog 1.8V block                           |

## 3 Absolute maximum ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2: Absolute Maximum Ratings

| Symbol             | Parameter                              | Min       | Max          | Units  | Comments                         |

|--------------------|----------------------------------------|-----------|--------------|--------|----------------------------------|

|                    | Elect                                  | rical Par | ameters      |        |                                  |

| VDD33              | 3.3V Supply Voltage to Ground          | -0.3      | 4.0          | V      |                                  |

| VDD18              | 1.8V Supply Voltage to Ground          | -0.3      | 2.3          | V      |                                  |

| V <sub>DLVDS</sub> | DC Voltage at LVDS START and STOP pins | -0.3      | VDD33+0.3    | V      |                                  |

| $V_{\text{DIO}}$   | ·                                      |           | VDD33+0.3    | V      |                                  |

| I <sub>SCR</sub>   | Input current (latch-up immunity)      | -100      | 100          | mA     | JESD78E                          |

| P <sub>tot</sub>   | Total Power Dissipation                |           | 150          | mW     |                                  |

|                    | Electr                                 | ostatic D | Discharge    |        |                                  |

| ESD <sub>HBM</sub> | Electrostatic Discharge HBM            | ± 2000    |              | V      | JS-001-2017                      |

| ESD <sub>CDM</sub> | Electrostatic Discharge CDM            | ± 500     |              | V      | JS-002-2018                      |

|                    | Temperature Ran                        | iges and  | Storage Cond | itions |                                  |

| T <sub>J</sub>     | Operating Junction Temperature         | -40       | 125          | °C     |                                  |

| T <sub>STRG</sub>  | Storage Temperature Range              | - 65      | 150          | °C     |                                  |

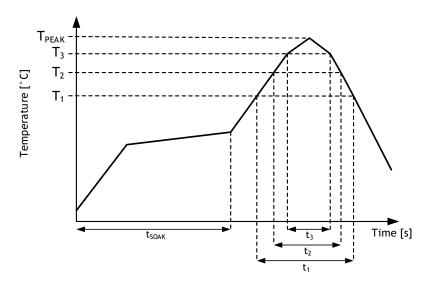

| $T_{BODY}$         | Package Body Temperature               |           | 260          | °C     | IPC/JEDEC J-STD-020 <sup>2</sup> |

| RH <sub>NC</sub>   | Relative Humidity (non-condensing)     | 5         | 85           | %      |                                  |

| MSL                | Moisture Sensitivity Level             | 3         |              |        | Maximum floor life time of 168h  |

<sup>&</sup>lt;sup>2</sup> (1) The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices." The lead finish for Pb free leaded packages is "Matte Tin" (100 % Sn)

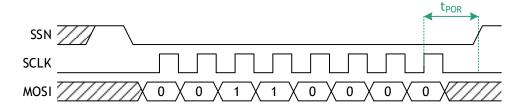

# 4 Recommended Operating Conditions

Recommended operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Test conditions for guaranteed specification are expressly denoted.

Table 3: Recommended operation conditions

| Symbol                 | Parameter                          | Conditions                          | Min                  | Тур  | Max       | Unit |

|------------------------|------------------------------------|-------------------------------------|----------------------|------|-----------|------|

|                        |                                    | Power Supply                        |                      |      |           |      |

| VDD33                  | DC Supply Voltage VDD33            |                                     | 3.0                  | 3.3  | 3.6       | V    |

| VDD18                  | DC Voltage at VDD18 pin            | Supplied from chip                  | 1.62                 | 1.8  | 1.98      | V    |

| t <sub>POR</sub>       | Startup time                       |                                     |                      | 10   |           | ms   |

|                        |                                    | Temperature                         |                      |      |           |      |

| T <sub>A</sub>         | Operating free air temperature (1) |                                     | -25                  | 25   | 105       | °C   |

|                        |                                    | Digital Inputs and Out              | puts                 |      |           |      |

| $V_{\text{IL},CMOS}$   | CMOS Input Low Voltage             |                                     |                      |      | 0.4       | V    |

| $V_{\text{IH,CMOS}}$   | CMOS Input High Voltage            |                                     | VDD33 –<br>0.4       |      |           |      |

| $t_{\text{p,minCMOS}}$ | Pulse width for detection          |                                     | 3.4                  |      |           | ns   |

| I <sub>leak</sub>      | Input leakage current              |                                     | -10                  |      | 10        | μΑ   |

| $C_{in}$               | Input capacitance                  |                                     |                      |      | 10        | pF   |

| $V_{OH}$               | High level output voltage          | I <sub>out</sub> = 24 mA            | 0.8 *<br>VDD33       |      |           | V    |

| $V_{OL}$               | Low level output voltage           | $I_{out} = 24 \text{ mA}$           |                      |      | 0.4       | V    |

| ILEAKTS                | Tri-state output leakage current   | V <sub>out</sub> = VDD33            | -10                  |      | 10        | μΑ   |

| $V_{\text{ID}}$        | Minimum differential input voltage |                                     | 100                  |      |           | mV   |

| V <sub>hys</sub>       | Hysteresis                         | LVDS<br>CMOS                        | 40<br>0.2*AVDD<br>33 |      |           | mV   |

| V <sub>ICM</sub>       | Common input voltage               | GND2 =A2GND18                       | VID/2                | 1.25 | 2.4-VID/2 | V    |

| $t_{p,min}$            | Pulse width for detection          |                                     | 2                    |      |           | ns   |

|                        |                                    | Oscillator                          |                      |      |           |      |

| Fosc                   | Oscillator Frequency               |                                     | 4                    | 10   | 20        | MHz  |

| DC                     | Duty cycle                         |                                     | 40                   |      | 60        | %    |

| I <sub>CC</sub>        | Current on V <sub>CC</sub>         | After initial startup               |                      |      | 0.9       | mA   |

| $I_{DD}$               | Current on V <sub>DD</sub>         |                                     |                      |      | 0.1       | mA   |

| T <sub>STUP</sub>      | Startup time                       | Settling at target frequency ±0.01% |                      |      | 10        | ms   |

| R <sub>START</sub>     | Internal feedback resistance       | info                                |                      | 1    |           | MΩ   |

| Current Consumption |                     |                    |  |     |    |  |

|---------------------|---------------------|--------------------|--|-----|----|--|

|                     | Standby current     |                    |  | 100 | μΑ |  |

|                     | Current after INIT  | No hits            |  |     | mA |  |

|                     | Measurement current | 100 ksps<br>1 Msps |  | 50  | mA |  |

<sup>(1)</sup> Recommended Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Test conditions for guaranteed specification are explicitly denoted.

# 5 Typical Characteristics

The following test levels apply to all following characteristics.

Table 4: Test levels

| Test Level | Description                                                                          |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| 1          | 100% production tested.                                                              |  |  |  |  |  |

| II         | 100% production tested at 25°C and guaranteed by design and characterization testing |  |  |  |  |  |

| Ш          | Parameter is guaranteed by design and characterization testing                       |  |  |  |  |  |

| IV         | Sample tested                                                                        |  |  |  |  |  |

| V          | Parameter is a typical value only.                                                   |  |  |  |  |  |

| 1          | 100% production tested.                                                              |  |  |  |  |  |

## 5.1 Converter Characteristics

General Conditions: VDD33 = 3.3 V; VDD18 = 1.8 V;  $T_A$  = 0 °C to 80 °C.

Table 5: Characteristics

| Symbol            | Description                          | Conditions                                                                                         | TL  | Min               | Тур             | Max               | Unit |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|-----|-------------------|-----------------|-------------------|------|

|                   |                                      | nents                                                                                              |     |                   |                 |                   |      |

| RMS               | Single-shot RMS resolution           | -25 to +85° C<br>High_Resolution = 0 (off)<br>High_Resolution = 1 (2x)<br>High_Resolution = 2 (4x) | IV  |                   | 30<br>25<br>20  | 45<br>37<br>30    | ps   |

| INL               | Integral non-linearity               |                                                                                                    | IV  |                   |                 | 20                | ps   |

| DNL               | Differential non-<br>linearity       |                                                                                                    | V   |                   | 5               |                   | ps   |

|                   | No missing code                      | At time quantization level                                                                         | Ш   | ,                 | Assured         |                   |      |

|                   | Channel to channel isolation         | At same times measured                                                                             | IV  |                   | 100             | 200               | ps   |

|                   | Offset between START and STOP1       |                                                                                                    | IV  |                   | 500             | <mark>1000</mark> | ps   |

|                   | Offset drift between START and STOP1 |                                                                                                    |     |                   |                 |                   | ps/K |

|                   | Offset error between STOP1 and STOP2 | error between High_Resolution = 0 (off) V                                                          |     | 100<br>150<br>200 |                 | ps                |      |

|                   | Offset drift between STOP1 and STOP2 | High_Resolution = 0 (off)<br>High_Resolution = 1 (2x)<br>High_Resolution = 2 (4x)                  | IV  |                   | 0.5<br>1<br>1.5 | 3                 | ps/K |

|                   |                                      | Switching Performance                                                                              |     |                   |                 |                   |      |

| t <sub>CONV</sub> | Converter latency (INT set)          | High_Resolution = 0 (off)<br>High_Resolution = 1 (2x)                                              | III |                   |                 |                   | ns   |

|   |                          | High_Resolution = 2 (4x)                                                    |     |     |                |      |

|---|--------------------------|-----------------------------------------------------------------------------|-----|-----|----------------|------|

| P | Peak conversion rate     | High_Resolution = 0 (off) High_Resolution = 1 (2x) High_Resolution = 2 (4x) | III |     | 50<br>20<br>10 | Msps |

|   | Maximal read-out<br>rate | SCK = 50MHz<br>Opcode + 48-Bit<br>Opcode + 16-Bit                           | III | 0.9 | 2.1            | Msps |

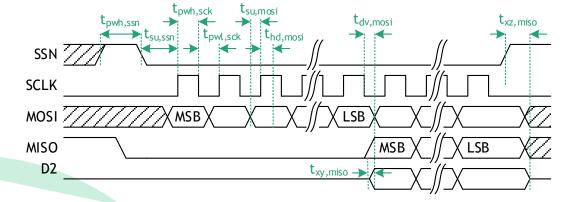

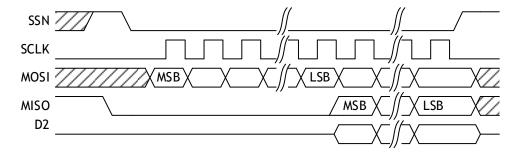

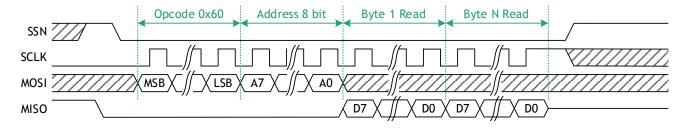

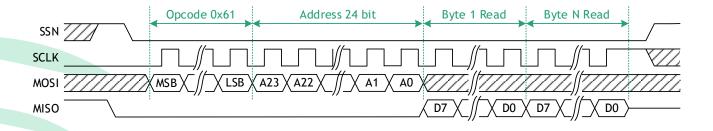

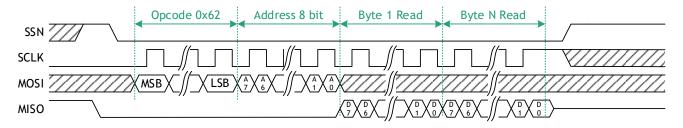

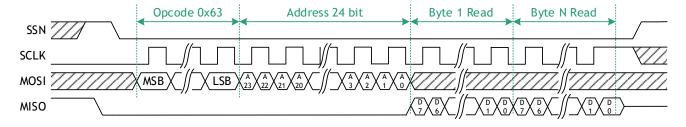

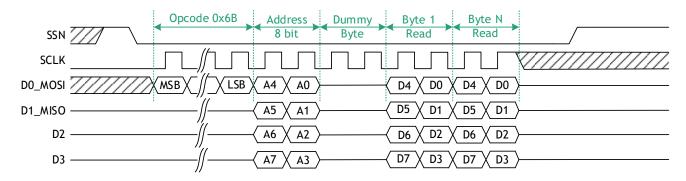

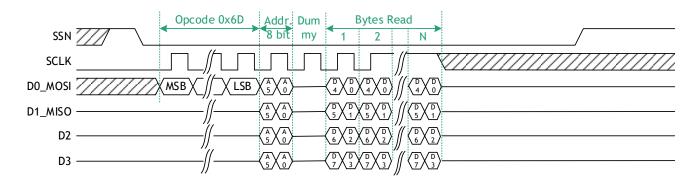

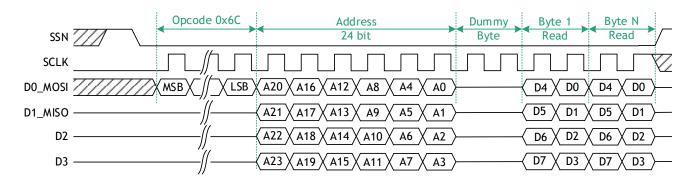

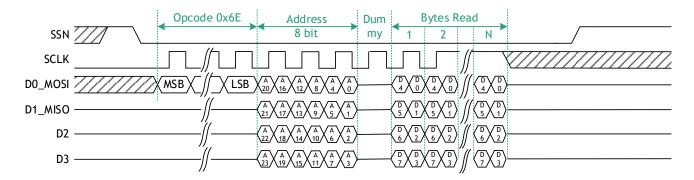

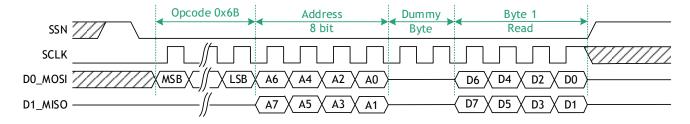

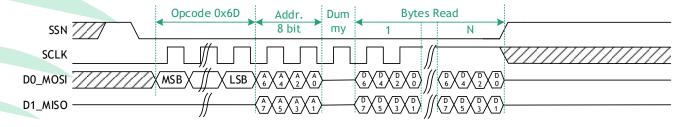

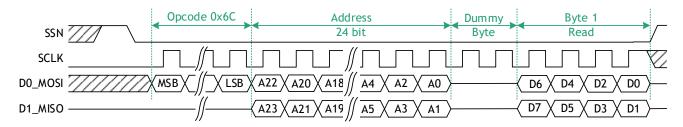

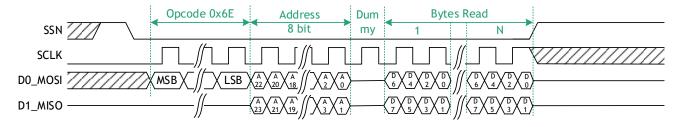

# 5.2 SPI Timings

SPI slave timing values are described in the following table (the measurement points are done at  $0.2 \cdot VDD$  and  $0.8 \cdot VDD$ ):

Table 6: SPI characteristics

| Symbol            | Parameter                            | Min   | Max | Units |

|-------------------|--------------------------------------|-------|-----|-------|

| f <sub>sck</sub>  | Serial clock frequency               |       | 50  | MHz   |

| $t_{\sf pwh,sck}$ | Serial clock pulse width HI state    | 10-5% |     | ns    |

| $t_{\sf pwl,sck}$ | Serial clock pulse width LO state    | 10-5% |     | ns    |

| $t_{\sf pwh,ssn}$ | SSN pulse width between write cycles | 20    |     | ns    |

| $t_{su,ssn}$      | SSN setup time before SCK rising     | 3     |     | ns    |

| $t_{hd,ssn}$      | SSN hold time after SCK rising       | 3     |     | ns    |

| $t_{su,mosi}$     | Data setup time prior to clock edge  | 2     |     | ns    |

| $t_{\sf hd,mosi}$ | Data hold time after clock edge      | 2     |     | ns    |

| $t_{ m dv,mosi}$  | Data valid after falling clock edge  |       | 8   | ns    |

| $t_{zx, miso}$    | HighZ to output time                 |       | 8   | ns    |

| $t_{xz,miso}$     | Output to HighZ time                 |       | 8   | ns    |

Figure 3: SPI Timings

# 6 Register description

This section describes the registers of the LTDC-X3, which enable the host system to

- Configure the LTDC-X3 and set the operating mode

- Read back the timing information

- Read back STATUS information

## 6.1 Register overview

Table 7: Register Overview

| Address      | Name          | Access | Description                                    |

|--------------|---------------|--------|------------------------------------------------|

| 0x00 to 0x0F | CFG0 TO CFG15 | RW     | TDC Configuration registers                    |

| 0x11         | WRN_LOCK      |        |                                                |

| 0x12         | ENC_SET       |        | OCDI configuration registers                   |

| 0x13         | COM_SET       |        | QSPI configuration registers                   |

| 0x14         | CH_CFG20      |        |                                                |

| 0x15 to 0x17 | TOF_CH1       |        | Result registers:                              |

| 0x18 to 0x1A | PW_CH1        |        | Time of flight channel 1                       |

| 0x1B to 0x1D | TOF_CH2       |        | Pulse width channel 1 Time of flight channel 2 |

| 0x1E to 0x20 | PW_CH2        |        | Pulse width channel                            |

| 0x21         | DEV_STATE     |        | Reserved                                       |

| 0x22         | TDC_STAT_REG1 |        |                                                |

| 0x23         | TDC_STAT_REG2 |        |                                                |

| 0x24         | TDC_STAT_REG3 |        | TDC Status                                     |

| 0x25         | TDC_STAT_REG4 |        |                                                |

| 0x26 to 0x28 | N.C.          |        |                                                |

| 0x2A to 0x2F | ANALOG_CFGX   |        | Analog Configuration                           |

| 0x30 to 0x33 | CALIB_CFGX    |        | Delay line calibration                         |

|              | TRIG_ID       |        |                                                |

|              | TRIG_NOISE    |        | Trigger configuration                          |

|              | TRIG_PERIOD   |        |                                                |

| 0x40 to 0x46 | N.C.          |        | Not used                                       |

Note: register addresses that are not listed here are not used and set by default to 0.

# 6.2 Detailed register description

## 6.2.1 CFG0 (Address 0x00)

Table 8: Register CFG0

| Addres | ss 0x00         | CFG0    | CFG0   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|--------|-----------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bits   | Field Name      | Default | Access | Field Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 7      |                 |         |        | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 6      | SSN_INIT_ENA    | 0x00    | RW     | Source of re-initialization of TDC:  0: SINGLE ACCESS individual read access with SSN possible TDC has to be restart by opcode TDC_REINIT or pin REINIT  1: DMA AUTOMATIC ACCESS SSN constantly at 0 during read-out TDC is restarted automatically when SSN is high again (and fifo are read out complete)? reinit if SSN=1 and INT=1 (read completed)? reinit if SSN=1 and INT=0 (read not completed) (tdb: STOP2?) Forced=alway possible: - reinit by opcode send by spireinit by pin |  |  |

| 5:4    | HIGHRES         | 0x00    | RW     | Settings for higher resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 3      | CHANNEL_COMBINE | 0x00    | RW     | Stop1 measured on one channel only     Stop1 measured on both stop channels alternately for halving pulse-to-pulse distance                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 2      |                 |         |        | Set 1. reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 1      | HIT_ENA_STOP2   | 0x00    | RW     | Software enable der Stop2 input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 0      | HIT_ENA_STOP1   | 0x00    | RW     | Software enable der Stop1 input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

## 6.2.2 CFG1 (Address 0x01)

Table 9: Register CFG1

| Address 0x01 |             | CFG1    |        |                                  |  |

|--------------|-------------|---------|--------|----------------------------------|--|

| Bits         | Field Name  | Default | Access | Field Description                |  |

| 7:6          |             |         |        | reserved                         |  |

| 5:3          | HITBUFSIZE2 | 0x00    | RW     | (application) hit buffer size 18 |  |

| 2:0          | HITBUFSIZE1 | 0x00    | RW     | (application) hit buffer size 18 |  |

## 6.2.3 CFG2 (Address 0x02)

Table 10: Register CFG2

| Addr | ess 0x02   | CFG2    |        |                                                                                                                                                                                                                                                                       |  |

|------|------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bits | Field Name | Default | Access | Field Description                                                                                                                                                                                                                                                     |  |

| 7:0  | TIMEOUT    | 0x00    | RW     | 8-bit timeout counter which is synchronized to the start pulse (100 ns uncertainty) and used for timeout of TDC, ToF and conversion. 0: timeout generation off 1: period of the reference clock 2: periods of the reference clock 255: periods of the reference clock |  |

## 6.2.4 CFG3 (Address 0x03)

Table 11: Register CFG3

| Address 0x03 |                     | CFG3    |        |                                                    |  |

|--------------|---------------------|---------|--------|----------------------------------------------------|--|

| Bits         | Field Name          | Default | Access | Command                                            |  |

| 7:0          | DELSTM_DLY<br>[7:0] | 0x00    | RW     | Delay for STOP mask. Counted in <b>DELTRIG_LSB</b> |  |

## 6.2.5 CFG4 (Address 0x04)

Table 12: Register CFG4

| Addre | ss 0x04              | CFG4    |        |                                                    |

|-------|----------------------|---------|--------|----------------------------------------------------|

| Bits  | Field Name           | Default | Access | Command                                            |

| 7:4   |                      |         |        | reserved                                           |

| 3:0   | DELSTM_DLY<br>[11:8] | 0x00    | RW     | Delay for STOP mask. Counted in <b>DELTRIG_LSB</b> |

## 6.2.6 CFG5 (Address 0x05)

Table 13: Register CFG3

| Address 0x03 | CFG5 |

|--------------|------|

|--------------|------|

| Bits | Field Name         | Default | Access | Command                                                                         |

|------|--------------------|---------|--------|---------------------------------------------------------------------------------|

| 7:0  | REFCLKDIV<br>[7:0] | 0x00    | RW     | Defines a LSB at the output interface as fraction of the reference clock period |

## 6.2.7 CFG6 (Address 0x06)

Table 14: Register CFG6

| Addre | ess 0x06            | CFG6    |        |                                                                                 |

|-------|---------------------|---------|--------|---------------------------------------------------------------------------------|

| Bits  | Field Name          | Default | Access | Command                                                                         |

| 7:0   | REFCLKDIV<br>[15:8] | 0x00    | RW     | Defines a LSB at the output interface as fraction of the reference clock period |

#### 6.2.8 CFG7 (Address 0x07)

Table 15: Register CFG7

| Address 0x07 CFG7 |                      |         |        |                                                                                 |

|-------------------|----------------------|---------|--------|---------------------------------------------------------------------------------|

| Bits              | Field Name           | Default | Access | Command                                                                         |

| 7:0               | REFCLKDIV<br>[23:16] | 0x00    | RW     | Defines a LSB at the output interface as fraction of the reference clock period |

## 6.2.9 CFG8 (Address 0x08)

Table 16: Register CFG8

| Addre | Address 0x08  |         | CFG8   |                                                                                                                                                                             |  |  |

|-------|---------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bits  | Field Name    | Default | Access | Command                                                                                                                                                                     |  |  |

| 7:6   | NOT USED      | 0x00    | RW     | Not used                                                                                                                                                                    |  |  |

| 5     | STOP_MASK_ENA | 0x00    | RW     | Enables noise mask or pin STOP_MASK for stop hits after hit on start input a configured time is wait, until the first stop hit is accepted 0: stops enabled 1: stops masked |  |  |

| 4     | STOP_MASK_EXT | 0x00    | RW     | Selects source of noise mask 0: by noise mask delay line 1: by noise mask pin                                                                                               |  |  |

| 3:2 | DELSTM_LSB  | 0x00 | RW | Length of LSB of stop mask as a fraction of the reference clock period:  3: 10/1024 * T <sub>ref</sub> (e.g.1 ns @ 10 MHz)     |

|-----|-------------|------|----|--------------------------------------------------------------------------------------------------------------------------------|

| 1:0 | DELTRIG_LSB | 0x00 | RW | Length of LSB of trigger delay as a fraction of the reference clock period: 0: 1/1024 * T <sub>ref</sub> (e.g.100 ps @ 10 MHz) |

## 6.2.10 CFG9 (Address 0x09)

#### Table 17: Register CFG9

| Addre | ess 0x09     | CFG9    |        |                                                               |

|-------|--------------|---------|--------|---------------------------------------------------------------|

| Bits  | Field Name   | Default | Access | Command                                                       |

| 7:0   | TRIG_MAX_DEL | 0x00    | RW     | Maximal delay count for tigger output in units of DELTRIG_LSB |

## 6.2.11 CFG10 to14 (Address 0x0A to 0x0D)

Address 0x0A: 63

Address 0x0B: 32+192

Address 0x0C: 37+64

Address 0x0D: 30+192

Address 0x0A: 35+192

#### 6.2.12 CFG15 (Address 0x0F)

Table 18: Register CFGF3

| Address 0x0F |            | CFG15   |        |                    |  |

|--------------|------------|---------|--------|--------------------|--|

| Bits         | Field Name | Default | Access | Command            |  |

| 7:0          | NOT USED   |         |        | Reserved, set 0x27 |  |

|              |            |         |        |                    |  |

|              |            |         |        |                    |  |

## 6.2.13 WRN\_LOCK (Address 0x11)

Table 19: Register WRN\_LOCK

| Addre | ess 0x11   | WRN_LOCH | (      |                                                                                                          |

|-------|------------|----------|--------|----------------------------------------------------------------------------------------------------------|

| Bits  | Field Name | Default  | Access | Command                                                                                                  |

| 0     | WRN_LOCK   | 0x1      | RW     | Write lock/unlock register 0: Functional registers are not writable 1: Functional registers are writable |

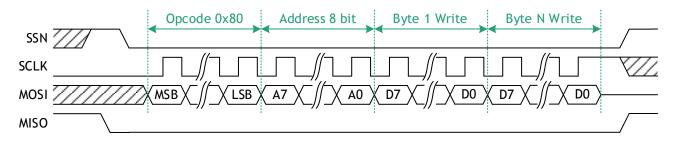

# 6.2.14 COM\_SET (Address 0x13)

Table 20: Register COM\_SET

| Addre | ss 0x13     | COM_SET |        |                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------|-------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits  | Field Name  | Default | Access | Command                                                                                                                                                                                                                                                                                                                                                                                             |

| 7:4   | DUMMY_CYCLE | 0x0     | RW     | Sets the number of dummy cycles inserted in the Dual SPI and Quad SPI communication. Values can range from 0 to up to 15 clock cycles 1 is typically recommended                                                                                                                                                                                                                                    |

| 3:2   | TR_MODE     | 0x0     | RW     | Transfer mode for reading from hit buffer:  0: Default mode. The slave reads three bytes of TOF and three bytes of PWSTOP  1:In this mode, the least significant bytes of TOF and PWSTOP are discarded, this leads to an increase in transmission speed at the expense of measurement accuracy.  2: In this mode, only the TOF is read and the PWSTOP is discarded. It is the fastest reading mode. |

| 1     | EN_DUAL     | 0x0     | RW     | Enables dual mode for the QSPI interface                                                                                                                                                                                                                                                                                                                                                            |

| 0     | EN_QUAD     | 0x0     | RW     | Enables quad mode for the QSPI interface                                                                                                                                                                                                                                                                                                                                                            |

## 6.2.15 CH\_CFG20 (Address 0x14)

Table 21: Register CH\_CFG20

| Addre | ess 0x14   | CH_CFG20 |        |                                                               |

|-------|------------|----------|--------|---------------------------------------------------------------|

| Bits  | Field Name | Default  | Access | Command                                                       |

| 7     | MASK_OV    | 0x1      | RW     | Overflow time (0xFFFFFE) in TOF will also mask PW with 0xFFFE |

| 6:3   | BUFF_SIZE  | 0xf      | RW     | Set to 15                                                     |

| 2:1 | CH_CFG  | 0x3 | RW | Channel read out configuration 0: OFF 1: read channel 1 only 2: read channel 2 only 3: read channel 1 & 2 alternatingly                                                                                                                                   |

|-----|---------|-----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | ACCMODE | 0x1 | RW | Defines the access mode.  0: Single access. The QSPI slave requires only one TOF and PWSTOP. read several times.  1: Incremental access. In this mode, the QSPI slave refreshes the TDC data every time it has completed the reading of the previous one. |

# 6.2.16 TOF\_CH1\_H (Address 0x15)

Table 22: Register TOF\_CH1\_H

| Addre | ess 0x15        | TOF_CH1_I | Н      |                                           |

|-------|-----------------|-----------|--------|-------------------------------------------|

| Bits  | Field Name      | Default   | Access | Command                                   |

| 7:0   | TOF_CH1 [23:16] | 0x00      | RO     | TDC channel 1 time-of-flight data [23:16] |

#### 6.2.17 TOF\_CH1\_M (Address 0x16)

Table 23: Register TOF\_CH1\_M

| Addre | ess 0x16       | TOF_CH1_I | VI     |                                          |

|-------|----------------|-----------|--------|------------------------------------------|

| Bits  | Field Name     | Default   | Access | Command                                  |

| 7:0   | TOF_CH1 [15:8] | 0x00      | RO     | TDC channel 1 time-of-flight data [15:8] |

## 6.2.18 TOF\_CH1\_L (Address 0x17)

Table 24: Register TOF\_CH1\_L

| Addre | ss 0x17       | TOF_CH1_l | -      |                                         |

|-------|---------------|-----------|--------|-----------------------------------------|

| Bits  | Field Name    | Default   | Access | Command                                 |

| 7:0   | TOF_CH1 [7:0] | 0x00      | RO     | TDC channel 1 time-of-flight data [7:0] |

#### 6.2.19 PW\_CH1\_H (Address 0x18)

Table 25: Register PW\_CH1\_H

|   | Addre | ss 0x18        | PW_CH1_H |        |                                        |

|---|-------|----------------|----------|--------|----------------------------------------|

|   | Bits  | Field Name     | Default  | Access | Command                                |

| Ī | 7:0   | PW_CH1 [23:16] | 0x00     | RO     | TDC channel 1 pulse width data [23:16] |

## 6.2.20 PW\_CH1\_M (Address 0x19)

Table 26: Register PW\_CH1\_M

| Addre | ess 0x19      | PW_CH1_L |        |                                       |

|-------|---------------|----------|--------|---------------------------------------|

| Bits  | Field Name    | Default  | Access | Command                               |

| 7:0   | PW_CH1 [15:8] | 0x00     | RO     | TDC channel 1 pulse width data [15:8] |

## 6.2.21 PW\_CH1\_L (Address 0x1A)

Table 27: Register PW\_CH1\_L

| Addre | ess 0x1A     | PW_CH1_L |        |                                      |

|-------|--------------|----------|--------|--------------------------------------|

| Bits  | Field Name   | Default  | Access | Command                              |

| 7:0   | PW_CH1 [7:0] | 0x00     | RO     | TDC channel 1 pulse width data [7:0] |

#### 6.2.22 TOF\_CH2\_H (Address 0x1B)

Table 28: Register TOF\_CH2\_H

| Addre | ss 0x1B         | TOF_CH2_I | 4      |                                           |

|-------|-----------------|-----------|--------|-------------------------------------------|

| Bits  | Field Name      | Default   | Access | Command                                   |

| 7:0   | TOF_CH2 [23:16] | 0x00      | RO     | TDC channel 2 time-of-flight data [23:16] |

#### 6.2.23 TOF\_CH2\_M (Address 0x1C)

Table 29: Register TOF\_CH2\_M

| Address 0x1C TOF_CH2_L |

|------------------------|

|------------------------|

| Bits | Field Name     | Default | Access | Command                                  |

|------|----------------|---------|--------|------------------------------------------|

| 7:0  | TOF_CH2 [15:8] | 0x00    | RO     | TDC channel 2 time-of-flight data [15:8] |

## 6.2.24 TOF\_CH2\_L (Address 0x1D)

Table 30: Register TOF\_CH2\_L

| Addre | ess 0x1D     | TOF_CH2_I | L                      |                                         |

|-------|--------------|-----------|------------------------|-----------------------------------------|

| Bits  | Field Name   | Default   | Default Access Command |                                         |

| 7:0   | TOF_C2 [7:0] | 0x00      | RO                     | TDC channel 2 time-of-flight data [7:0] |

## 6.2.25 PW\_CH2\_H (Address 0x1E)

## Table 31: Register PW\_CH2\_H

| Addre | ess 0x1E       | PW_CH2_H | PW_CH2_H               |                                        |  |

|-------|----------------|----------|------------------------|----------------------------------------|--|

| Bits  | Field Name     | Default  | Default Access Command |                                        |  |

| 7:0   | PW_CH2 [23:16] | 0x00     | RO                     | TDC channel 2 pulse width data [23:16] |  |

## 6.2.26 PW\_CH2\_M (Address 0x1F)

## Table 32: Register PW\_CH2\_M

| Addre | ess 0x1F      | PW_CH2_L |                        |                                       |

|-------|---------------|----------|------------------------|---------------------------------------|

| Bits  | Field Name    | Default  | Default Access Command |                                       |

| 7:0   | PW_CH2 [15:8] | 0x00     | RO                     | TDC channel 2 pulse width data [15:8] |

## 6.2.27 PW\_CH2\_L (Address 0x20)

#### Table 33: Register PW\_CH2\_L

| Ad  | ldre | ss 0x20      | PW_CH2_L |                |                                      |

|-----|------|--------------|----------|----------------|--------------------------------------|

| Bit | ts   | Field Name   | Default  | Access Command |                                      |

| 7:0 | )    | PW_CH2 [7:0] | 0x00     | RO             | TDC channel 2 pulse width data [7:0] |

## 6.2.28 DEV\_STATE (Address 0x21)

Table 34: Register DEV\_STATE

| Addre | ess 0x21   | DEV_STAT | ГЕ     |                                                                                                                                           |

|-------|------------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Bits  | Field Name | Default  | Access | Command                                                                                                                                   |

| 1:0   | DEV_STATE  | 0x00     | RO     | Device status bits 1: Power-on reset was released 2: Configuration registers need to be written 3: Calibration is done, start measurement |

#### 6.2.29 TDC\_STAT\_REG1 (Address 0x22)

Table 35: Register TDC\_STAT\_REG1

| Addre | ess 0x22   | TDC_STA | T_REG1 |                             |

|-------|------------|---------|--------|-----------------------------|

| Bits  | Field Name | Default | Access | Command                     |

| 5     | EF_STO2_R  | 0x00    | RO     | Stop rise 2 FIFO flag empty |

| 4     | FF_STO2_R  | 0x00    | RO     | Stop rise 2 FIFO flag full  |

| 3     | EF_STO1_R  | 0x00    | RO     | Stop rise 1 FIFO flag empty |

| 2     | FF_STO1_R  | 0x00    | RO     | Stop rise 1 FIFO flag full  |

| 1     | EF_STA_R   | 0x00    | RO     | Start FIFO flag empty       |

| 0     | NOT USED   |         |        |                             |

## 6.2.30 TDC\_STAT\_REG2 (Address 0x23)

Table 36: Register TDC\_STAT\_REG2

| Addre | ess 0x23   | TDC_STA | T_REG2 |                             |

|-------|------------|---------|--------|-----------------------------|

| Bits  | Field Name | Default | Access | Command                     |

| 3     | EF_STO2_F  | 0x00    | RO     | Stop fall 2 FIFO flag empty |

| 2     | FF_STO2_F  | 0x00    | RO     | Stop fall 2 FIFO flag full  |

| 1     | EF_STO1_F  | 0x00    | RO     | Stop fall 1 FIFO flag empty |

| 0     | FF_STO1_F  | 0x00    | RO     | Stop fall 1 FIFO flag full  |

## 6.2.31 TDC\_STAT\_REG3 (Address 0x24)

Table 37: Register TDC\_STAT\_REG3

| Addre | ess 0x24    | TDC_STA | TDC_STAT_REG3 |                                                |  |

|-------|-------------|---------|---------------|------------------------------------------------|--|

| Bits  | Field Name  | Default | Access        | Command                                        |  |

| 6:4   | HITCNT_CH2R | 0x00    | RO            | Number of hits for rising edge in hit buffer 2 |  |

| 2:0   | HITCNT_CH1R | 0x00    | RO            | Number of hits for rising edge in hit buffer 1 |  |

## 6.2.32 TDC\_STAT\_REG4 (Address 0x25)

Table 38: Register TDC\_STAT\_REG4

| Addre | ess 0x25    | TDC_STA | TDC_STAT_REG4 |                                                 |  |

|-------|-------------|---------|---------------|-------------------------------------------------|--|

| Bits  | Field Name  | Default | Access        | Command                                         |  |

| 6:4   | HITCNT_CH2F | 0x00    | RO            | Number of hits for falling edge in hit buffer 2 |  |

| 2:0   | HITCNT_CH1F | 0x00    | RO            | Number of hits for falling edge in hit buffer 1 |  |

## 6.2.33 ANALOG\_CFG0 (Address 0x2A)

Table 39: Register ANALOG\_CFG0

| Addre | ess 0x2A    | ANALOG_ | ANALOG_CFG0 |                           |  |

|-------|-------------|---------|-------------|---------------------------|--|

| Bits  | Field Name  | Default | Access      | Command                   |  |

| 7     | REGBIAS_SEL | 0xC0    | RW          | Regulation bias selection |  |

| 6:4   | LDOTRIM     |         | RW          | LDO regulator trimming    |  |

| 3:0   | BGTRIM      |         | RW          | Bandgap trimming          |  |

#### 6.2.34 ANALOG\_CFG1 (Address 0x2B)

Table 40: Register ANALOG\_CFG1

| Address 0x2B |

|--------------|

|--------------|

| Bits | Field Name | Default | Access | Command                       |

|------|------------|---------|--------|-------------------------------|

| 7    | REF_SEL    | 0x04F   | RW     | XTAL reference load selection |

| 6:4  | GM_SEL     |         | RW     | XTAL drive strength selection |

| 3:0  | BIAS_SEL   |         | RW     | XTAL bias current selection   |

## 6.2.35 ANALOG\_CFG2 (Address 0x2C)

Table 41: Register ANALOG\_CFG2

| Addre | ess 0x2A           | ANALOG         | _CFG0 |                                       |

|-------|--------------------|----------------|-------|---------------------------------------|

| Bits  | Field Name         | Default Access |       | Command                               |

| 7     | CLAMP_DIS_START    | 0x16           | RW    | lvds configuration                    |

| 6     | fscmp_ena_start    |                | RW    | lvds configuration                    |

| 5     | thresoft_ena_start |                | RW    | lvds configuration                    |

| 4:3   | hysthigh_start     |                | RW    | lvds start channel hysterisys setting |

| 2:0   | reg_sel            |                | RW    | xtal current strength selection       |

## 6.2.36 ANALOG\_CFG3 (Address 0x2D)

Table 42: Register ANALOG\_CFG3

| Addre | ss 0x2D            | ANALOG_CFG3 |        |                    |

|-------|--------------------|-------------|--------|--------------------|

| Bits  | Field Name         | Default     | Access | Command            |

| 7     | thresoff_ena_stop2 | 0x42        | RW     | lvds configuration |

| 6     | hysthigh_stop2     |             | RW     | lvds configuration |

| 5     | hystdis_stop2      |             | RW     | lvds configuration |

| 4     | clamp_dis_stop1    |             | RW     | lvds configuration |

| 3     | fscmp_ena_stop1    |             | RW     | lvds configuration |

| 2     | thresoff_ena_stop1 |             | RW     | lvds configuration |

| 1     | hysthigh_stop1     |             | RW     | lvds configuration |

| 0 | hystdis_stop1 |  | RW | lvds configuration |

|---|---------------|--|----|--------------------|

|---|---------------|--|----|--------------------|

## 6.2.37 ANALOG\_CFG4 (Address 0x2E)

Table 43: Register ANALOG\_CFG4

| Addre | ess 0x2E        | ANALOG_        | CFG4 |                    |

|-------|-----------------|----------------|------|--------------------|

| Bits  | Field Name      | Default Access |      | Command            |

| 7:2   | NOT_USED        | 0x00           | RW   | Not used           |

| 1     | clamp_dis_stop2 | 0x00           | RW   | lvds configuration |

| 0     | fscmp_ena_stop2 | 0x00           | RW   | lvds configuration |

#### 6.2.38 ANALOG\_CFG5 (Address 0x2F)

Table 44: Register ANALOG\_CFG5

| Addre | ess 0x2F       | ANALOG_CFG5    |    |                                                 |

|-------|----------------|----------------|----|-------------------------------------------------|

| Bits  | Field Name     | Default Access |    | Command                                         |

| 7     | CMOS_ENA_STOP2 | 0x00           | RW | Enable CMOS threshold for STOP2 input           |

| 6     | CMOS_ENA_STOP1 | 0x00           | RW | Enable CMOS threshold for STOP1 input           |

| 5     | CMOS_ENA_START | 0x00           | RW | Enable CMOS threshold for START input           |

| 4     | LVDS_ENA_STOP2 | 0x00           | RW | Enable LVDS receiver STOP2                      |

| 3     | LVDS_ENA_STOP1 | 0x00           | RW | Enable LVDS receiver STOP1                      |

| 2     | LVDS_ENA_START | 0x00           | RW | Enable LVDS receiver START                      |

| 1     | OSC_ENA        | 0x00           | RW | Oscillator enable                               |

| 0     | IREF_ENA       | 0x00           | RW | Enable reference current source for LVDS, set 1 |

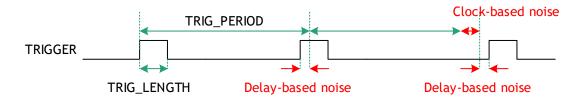

## 6.2.39 TRIG\_NOISE (Address 0x3CB)

Table 45: Register TRIG\_NOISE

| Address 0x3B | TRIG_NOISE |

|--------------|------------|

|--------------|------------|

| Bits | Field Name  | Default | Access | Command                                    |

|------|-------------|---------|--------|--------------------------------------------|

| 6:5  | TRIG_NOISE  | 0x00    | RW     | Defines the amplitude of the trigger noise |

| 4:1  | TRIG_LENGTH | 0x00    | RW     | Defines the length of the trigger pulse    |

| 0    | TRIG_ON     | 0x00    | RW     | 1: enables the trigger                     |

## 6.2.40 TRIG\_PERIOD (Address 0x3C)

Table 46: Register TRIG\_PERIOD

| Addre | ess 0x3C    | TRIG_PERIOD    |    |                                                                                                                                                                                                                         |

|-------|-------------|----------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits  | Field Name  | Default Access |    | Command                                                                                                                                                                                                                 |

| 7:0   | TRIG_PERIOD | 0x00           | RW | 8-bit counter which defines the duration of trigger period in multiples of the reference clock period 0: off 1: one trigger pulse every reference clock period 255: one trigger pulse every 255 reference clock periods |

# 7 Detailed Description

LTDC-X3 is a high-speed, high-resolution TDC designed specially for LiDAR applications. It is based on TDC-GPX2 architecture with a continuously running core, but with a dedicated measurement sequence like a start-stop TDC, starting with the initialization, waiting for hits on the START and STOP inputs, and ending with the interrupt when all hits or a timeout have been detected. It calculates STOP - START time differences and the width of the STOP pulses directly on the chip. LVDS inputs enable an easy integration into fast analog front ends. The QSPI (quad SPI) interface allows high sample rate and data readout via a standard interface.

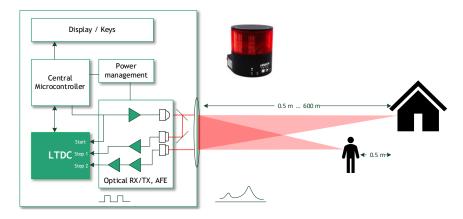

Figure 4: Application diagram

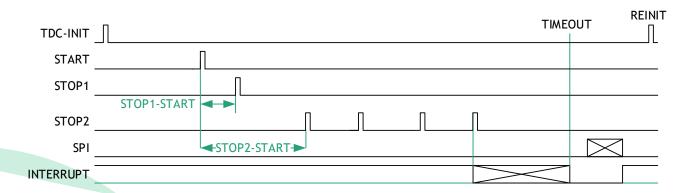

After configuration the chip will be initialized with the receipt of the SPI opcode TDC-INIT. The core is started and the TDC is ready to accept hits. The chip has a START input and two STOP inputs. It calculates the time differences between the STOP channels and the START channel. Time measurements are continuously calibrated against a reference clock which is generated from a 4 to 20 MHz quartz connected to the REFCLK pins. In typical LiDAR designs the START will be triggered by the laser trigger, STOP1 by, the reference beam and STOP2 will be the main measurement channel. On both channels the chip measures rising and falling edge and therefore the time-of-flight and the pulse width for each hit.

Figure 5: Measurement sequence

The number of expected hits can be configured, and as soon as those are receipt or a timeout occurred an interrupt is set and the external DSP can read the data. The measurement cycle is finished by an automatic or external (SPI or pin) re-initialization which arms the chip for the next measurement.

The reinitialization can be triggered by various sources:

- FIFOs are read

- Interrupt and QSPI-SSN are back to high

- Pulse on pin REINIT at any time

- SPI command

## 7.1 Input Structure for Time Measurement

The inputs for START, STOP1 and STOP2 are built with LVDS differential line receivers designed for applications requiring high data rates. They accept differential input signals and translate them to CMOS output levels. The 1000hm differential input termination is not provided internally, therefore 500hm transmission lines and the external termination resistor are needed at pcb level.

The LVDS inputs can be used as single ended receivers to emulate CMOS inputs just connecting the negative input to VDD18 at pcb level. Switching thresholds will be about +/-50 mV around VDD18 without requiring a configuration bit.

The minimum pulse width for the input signals to pass these first comparators is typ. 2 ns for LVDS and 3 ns for CMOS. Shorter pulses might not set the output level high and the hits will be disappear and not trigger the next functional blocks.

#### 7.1.1 START

The base value for START should be zero. The first rising edge on pin START after initialization acts as start time for the TDC measurement and the noise mask window. For operation, the pin has to be enabled. Following configuration bits are relevant:

Table 47: START configuration

| Register         | Bit | Parameter      | Descrition                                      |

|------------------|-----|----------------|-------------------------------------------------|

| 0x2E ANALOG_CFG5 | 5   | CMOS_ENA_START | 1: enables the CMOS threshold for the START     |

|                  | 2   | LVDS_ENA_START | 1: enables the LVDS START receiver              |

|                  | 0   | IREF_ENA       | 1: enables the reference in case of LVDS inputs |

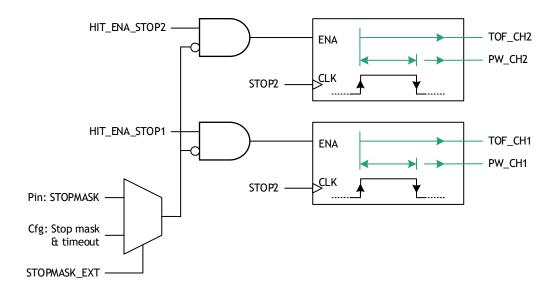

#### 7.1.2 STOP1, STOP2

The base value of the stop signal inputs should be zero and the stop pulses high active. The rising and falling edges of the stop signals are measured versus rising edge of the start pulse. The chip has two independent stop channels. With CHANNEL\_COMBINE variations of this normal operation mode can be achieved. For operation, the pins have to be enabled. Following configuration bits are relevant:

Table 48: STOP configuration

| Register         | Bit | Parameter       | Descrition                                                                              |

|------------------|-----|-----------------|-----------------------------------------------------------------------------------------|

| 0x2E ANALOG_CFG5 | 7   | CMOS_ENA_STOP2  | 1: Enables the CMOS threshold for the STOP2                                             |

|                  | 6   | CMOS_ENA_STOP1  | 1: Enables the CMOS threshold for the STOP1                                             |

|                  | 4   | LVDS_ENA_STOP2  | 1: Enables the LVDS STOP2 receiver                                                      |

|                  | 3   | LVDS_ENA_STOP1  | 1: Enables the LVDS STOP1 receiver                                                      |

|                  | 0   | IREF_ENA        | 1: Enables the reference in case of LVDS inputs                                         |

| 0x00 <b>CFG0</b> | 3   | CHANNEL_COMBINE | 1: Stop1 measured on both stop channels alternately for halving pulse-to-pulse distance |

|                  | 2   |                 | Set 1. reserved                                                                         |

|                  | 1   | HIT_ENA_STOP2   | 1: Software enable of STOP2 input                                                       |

|                  | 0   | HIT_ENA_STOP1   | 1: SEoftware enable of STOP1 input                                                      |

Figure 6: Stop inputs logic

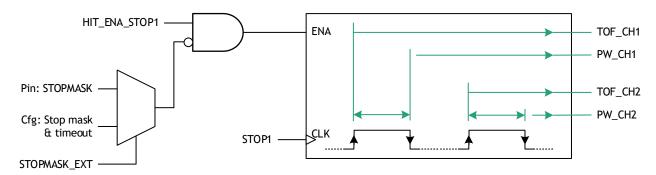

#### 7.1.2.1 Channel Combination for Low Pulse-to-Pulse Spacing

With **CHANNEL\_COMBINE** = **3** the two stop channels 1 & 2 are connected to one input pin STOP1. The stop pulses at the input pin are distributed alternatingly between the combined channels.

The advantages of combining channels lie in

- Excellent pulse-to-pulse spacing

- Keeping excellent pulse width definition

Doubled BUFFER depth for stop input pin

Figure 7: Channels 1 & 2 combined

#### 7.1.3 STOPMASK

There is a dedicated CMOS input pin for a stop mask signal. With setting stop mask pin to HIGH the measurement is suppressed on both stops channels. With setting stop mask pin to LOW the measurement is enabled on both stop channels. The STOPMASK pin an alternative for internal stop mask window configured with STOP\_MASK and TIMEOUT.

Table 49: STOP MASK configuration

| Register         | Bit           | Parameter                                                                     | Descrition                                                                                                                                                                  |

|------------------|---------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x08 <b>CFG8</b> | 5             | STOP_MASK_ENA                                                                 | Enables noise mask or pin STOP_MASK for stop hits after hit on start input a configured time is wait, until the first stop hit is accepted 0: stops enabled 1: stops masked |

| 4                | STOP_MASK_EXT | Selects source of noise mask 0: by noise mask delay line 1: by noise mask pin |                                                                                                                                                                             |

#### 7.1.4 REF\_OSC

The oscillator provides the master clock to the digital core. A biasing resistor is used to guarantee proper biasing points at DC. If lower value is needed an external resistor can be added.

Note: the oscillator is meant to deliver full performance in the primary operating range. In the "undervoltage" condition the oscillator will be functional but there could be a degradation of the performances.

The reference clock serves as universal time base. Due to internal averaging, the phase jitter of the reference clock is non-critical. The accuracy and drift of the reference clock will not affect the proper working of LTDC-X3 itself, but it will directly affect the time measurement results as they all are calibrated against the reference clock. It is possible to connect a quartz crystal or a ceramic resonator. But certainly, the selection will directly affect the quality of the time measurement results.

When the crystal driver is disabled, an external oscillator can be used for test purposes. The external clock shall be applied to the XTAL2 pin, while XTAL1 is tied to ground.

Table 50: Oscillator

| Register                | Bit | Parameter | Descrition            |

|-------------------------|-----|-----------|-----------------------|

| 0x2F <b>ANALOG_CFG5</b> | 1   | OSC_ENA   | 1: Oscillator enabled |

## 7.2 Start-up Sequence

- Apply/send POR reset.

- Configure the chip, including reference oscillator enable.

- In case the trigger output is used: send spi\_DELTRIG\_cal and wait for 50 ms to calibrate the delay line.

- In case the noise mask is used: send spi\_delstm\_cal and wait 50 ms for calibration.

- Start the measuring sequence by sending tdc\_init.

- The chip waits for synchronization of REFCLK

- The chip enables the TDC and waits 20 periods of the reference clock

- The chip enables the START channel

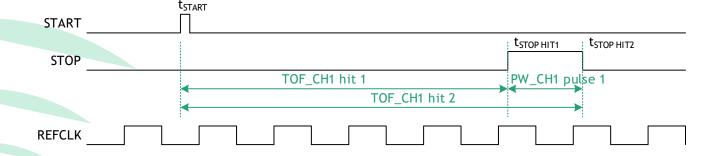

#### 7.3 Time Measurements and Results

The reference clock is the framework for all time measurements. Internally, all events (START, rising and falling edges at STOPX) are measured against the reference clock. TTD automatically calculates the time differences between STOP and START and calibrates those against the reference clock. Optionally, the pulse width can be calculated. The user reads the calibrated 24-bit results as TOF\_CHx and PW\_CHx, where PW could be the pulse width or the time for the falling edge.

- t<sub>START</sub> is the internal TDC measurement of a start pulse

- t<sub>STOP</sub> is the internal TDC measurement of a stop pulse

- t<sub>REF</sub> is the internal TDC measurement of the reference clock period to calibrate the results

- TOF\_CH1 is the time difference from START

- PW\_CH1 is the pulse width of the hit or the time difference to START for the falling edge

#### Figure 8: Time Measurement

#### 7.3.1 Reinitialization

The LTDC-X3 needs to be re-initialized for each measurement. To do this there are several options:

- Initialization only when all data were read out of the hit buffer and the interrupt went back to high (SSN\_INIT\_EN = 1: EFLAG = 1, SSN="goes back to one" = "rising edge").

- Via SPI opcode TDC-REINIT, independent from hit buffer fill state, possible even during an active measuring sequence.

- Automatically on a rising edge on SSN pin, even if valid data are still in the buffer .

- Positive pulse on pin REINIT.

#### 7.3.2 Stop Mask

Besides the pin STOPMASK there is a digital delay line that can be used to mask stops internally. This stop masks begins with a valid START and releases the STOP input after the configured time interval. This helps to suppress noise or short range signals. The range can be configured from 0 to 255 ns in steps of 1ns.

During start-up delay line has to calibrate by sending opcode spi\_delstm\_cal. Calibration should be repeated from time to time, especially if temperature varies. The following parameters are important for the configuration:

Table 51: Stop mask

| Register     |                              | Bit         | Parameter     | Descrition                                                                                                                                                                                               |  |  |

|--------------|------------------------------|-------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0x03<br>0x04 | CFG3<br>CFG4                 | 7:0<br>11:8 | DELSTM_DLY    | Delay for STOP mask. Counted in <b>DELSTM_LSB</b> , 0 to 4095                                                                                                                                            |  |  |

| 0x08         | CFG8                         | 3:2         | DELSTM_LSB    | LSB as fraction of reference clock period 0: 1/1024 * T <sub>ref</sub> (e.g.100 ps @ 10 MHz) 1: 2/1024 * T <sub>ref</sub> 2: 5/1204 * T <sub>ref</sub> 3: 10/1024 * T <sub>ref</sub> (e.g.1 ns @ 10 MHz) |  |  |

|              |                              | 5           | STOP_MASK_ENA | 1:= enable the STOP mask                                                                                                                                                                                 |  |  |

|              |                              | 4           | STOP_MASK_EXT | 0: source is an internal delay line 1: mask via STOPMASK pin.                                                                                                                                            |  |  |

| ST           | STARTt_stop hit1 t_stop hit2 |             |               |                                                                                                                                                                                                          |  |  |

STOPMASK

Figure 9: Stop Masking

#### 7.3.3 Timeout

The timeout defines the measurement range by setting a time limit before which the set number of hits shout have been arrived. If not enough hits are there the timeout sets the interrupt. Typically the limit is 2  $\mu$ s for 300m range. It is set in parameter **TIMEOUT**, register 2.

Table 52: Timeout

| Reg | giste | er   | Bit | Parameter | Descrition                                                                                                                                                 |

|-----|-------|------|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0 | 02    | CFG2 | 7:0 | TIMEOUT   | 8-BitTimeout counter, synchronized to start. 0: timeout generation off 1: One period of the reference clock 255: maximum 255 periods of the refrence clock |

The start of timeout counter is synchronized to start pulse. This means that there is an uncertainty in the timeout window of one period of the reference clock.

#### 7.3.4 Interrupt

Each TDC measurement is stored in the internal hit buffer. The buffer size is configurable. A low level at the interrupt pin indicates to the external microcontroller that the measurement is done and valid data are available. This occurs either if the last accepted stop hit has filled the configured buffer space or when a timeout has occurred.

The interrupt kept low until all data in the data buffer is read out. It is indicated via the interrupt pin.

#### 7.3.5 High Resolution Mode

In high resolution mode the stop events are internally delayed and measured several times. The standard deviation is reduced by this method, but as a trade of the pulse-pair resolution is worse.

Table 53: High resolution mode

| Registe | r    | Bit | Parameter | Descrition                                                                                                                                                                                       |

|---------|------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00    | CFG0 | 5:4 | HIGHRES   | Multiply the STOP hits internally for higher resolution 0: off standard resolution with minimal pulse-to-pulse spacing. 1: a stop event is measured twice 2: a stop event is measured four times |

#### 7.3.6 TDC Result

The output result TSTOP is the ratio of the internal measured times of  $t_{STOP}$  over  $t_{REF}$  scaled by the configured REFCLKDIV. These measurements and calculations are done automatically inside of the chip. The read-out result is in multiple of the configured LSB. The LSB is given by the ratio of the refence clock period over the configured REFCLKDIV. The LSB at the output interface should be chosen lower than the single shot resolution of the LTDC-X3. Suitable values are e.g., 1 ps, 5 ps or 10 ps.

$$t_{STOP} = TOF\_CHx \times LSB = TOF\_CHx \times \frac{T_{refclk}[ps]}{REFCLKDIV}$$

or  $TOF\_CHx = \frac{t_{STOP}}{T_{refclk}} \times REFCLKDIV$

Figure: Time Calculation

#### 7.3.7 Hit Buffer

Time measurement data are stored in two hit buffers, each with maximum 16 events. Per channel this means 8 time data and 8 pulse width data can be stored. The hit buffer size can be configured from 1 to 8. When the two channels are combined the buffer size reaches from 2 to 16.

Table 54: Hit buffer configuration

| Registe | er              | Bit | Parameter   | Descrition                                      |

|---------|-----------------|-----|-------------|-------------------------------------------------|

| 0x01    | CFG1            | 5:3 | HITBUFSIZE2 | Number of hits allowed/expected in hit buffer 2 |

|         | 2:0 HITBUFSIZE1 |     | HITBUFSIZE1 | Number of hits allowed/expected in hit buffer 1 |

The fill levels of the hit buffers are indicated in the status registers TDC\_STSA\_REG1 to ...REG3.

EF\_STA\_R Empty flag for START channel with rising edge

EF\_STOx\_y Empty flag for channel x with slope y

FF\_STOx\_y Full flag for channel x with slope y

FCNT\_STOx\_y Hit counter for channel x with slope y

The content of the hit buffers is read from registers 0x15 to 0x20 which hold the values for